-

摘要:

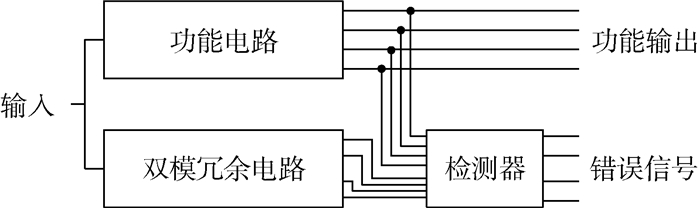

针对胚胎电子细胞阵列在线故障检测设计困难、检测率低、检测率难以准确计算等问题,提出了一种基于双模冗余的在线故障检测方法和一种基于电路等价性验证的故障检测率分析方法。设计了一种适用于查找表型功能单元的新型检测器,并开发了自动化设计程序。针对单固定型故障,将电路转变为待验证电路,再通过故障注入和等价性验证,可以快速精确地计算电路的故障检测率。仿真实验选取16个不同规模的标准电路,分别映射在胚胎电子细胞阵列中,分析了双模冗余后面积、延时变化情况和双模冗余的故障检测率。仿真结果给出了较为详细的面积消耗、电路延时和故障检测率等数据,并验证了本文方法具有很高的故障检测率。

Abstract:In order to solve the problems for embryonics array that online fault detection is difficult to be designed, detection rate is low, and detection rate is difficult to be accurately calculated, an online fault detection method based on dual modular redundancy and a fault detection rate analysis method based on equivalence checking are proposed. A novel checker which is suitable for look up table style function module of embryonics cell is designed, and the automated design program is developed. For single stuck at fault, the circuit is first converted to an equivalence checking circuit, and then through fault injection and equivalence checking, fault detection rate can be accurately calculated. In simulations, 16 different sizes of benchmark circuits are chosen, and mapped into embryonics array. Area, delay and fault detection rate of the dual modular redundancy circuit are analyzed. Simulation results are presented with detailed area consumption data, circuit delay data and fault detection rate data, and verify that the proposed method has a high fault detection rate.

-

表 1 故障检测方法比较

Table 1. Comparison of fault detection methods

检测方法 故障检测率 检测速度 资源消耗 适用范围 设计难度 DMR 高 实时 较大 无限制 低 TMR 高 实时 大 无限制 低 EDC 中等 实时 较小 一般用于组合电路 中等 LD 低 较快 中等 经特殊设计的电子阵列 高 AIS 较高 较快 小 小规模电路 中等 Roving STARs 高 慢 小 可重构电子阵列 高 表 2 电路规模、面积增长率和延时增长率

Table 2. Circuit scale, area increase rate and delay increase rate

电路 电路规模 触发器个数 输出个数 输入个数 AIR DIR c8 7×7 18 28 2.423 8 1.374 1 dk14 7×7 3 5 4 2.201 1 1.019 2 c499 9×9 32 41 2.584 3 1.347 2 s344 9×9 15 11 10 2.113 5 1.075 9 term1 10×10 10 34 2.148 4 1.202 4 s641 10×10 19 23 36 2.364 1 1.368 3 apex7 11×11 49 37 2.239 0 1.318 4 s820 11×11 5 19 19 2.343 0 1.190 1 c432 12×12 7 36 2.041 8 1.111 8 ex1 12×12 5 19 10 2.188 1 1.991 0 c880 14×14 26 60 2.258 8 1.470 6 s1 14×14 5 6 9 2.013 1 0.973 2 rot 18×18 135 107 2.482 3 1.353 0 s1494 18×18 6 19 9 2.113 2 1.198 2 c3540 21×21 22 50 2.031 0 1.314 5 scf 21×21 7 56 28 2.287 6 1.266 7 表 3 标准电路的故障检测率

Table 3. Fault detection rate of some benchmark circuits

电路 功能电路 检测电路 LUT FDR 触发器FDR LUT ST 触发器ST s-a-0 s-a-1 s-a-0 s-a-1 s-a-0 s-a-1 s-a-0 s-a-1 c8 100 100 100 100 c432 100 100 100 100 c499 100 100 100 100 term1 100 100 100 99.0 apex7 100 100 97.8 100 c880 100 100 100 100 rot 100 100 99.3 99.3 c3540 100 100 100 100 dk14 100 100 100 100 100 100 100 100 s344 100 100 100 100 98.7 98.7 100 100 s641 100 100 100 100 87.5 96.4 78.9 100 s820 100 100 100 100 100 100 100 100 ex1 100 100 100 100 100 100 100 100 s1 100 100 100 100 81.6 99.5 100 100 s1494 100 100 100 100 100 100 100 100 scf 100 100 100 100 99.2 100 100 100 -

[1] MANGE D, SANCHEZ E, STAUFFER A, et al.Embryonics:A new methodology for designing field-programmable gate arrays with self-repair and self-replicating[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 1998, 6(3):387-399. [2] KIM S, CHU H, YANG I, et al.A hierarchical self-repairing architecture for fast fault recovery of digital systems inspired from paralogous gene regulatory circuits[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2012, 20(12):2315-2328. [3] PRODAN L, UDRESCU M, VLADUTIU M, et al.Self-repairing embryonic memory arrays[C]//Proceedings 2004 NASA/DoD Conference on Evolvable Hardware.Piscataway, NJ:IEEE Press, 2004:130-137. [4] YANG S S, WANG Y R.A new self-repairing digital circuit based on embryonic cellular array[C]//Proceedings 2006 8th International Conference on Solid-State and Integrated Circuit Technology.Piscataway, NJ:IEEE Press, 2006:1997-1999. [5] BRADLEY D, CESAR O S, TYRRELL A.Embryonics+Immunotronics:A bio-inspired approach to fault tolerance[C]//Proceedings of the 2nd NASA/DoD Workshop on Evolvable Hardware.Piscataway, NJ:IEEE Press, 2000:215-223. [6] 郝国锋, 王友仁, 张砦, 等.可重构硬件芯片级故障定位与自主修复方法[J].电子学报, 2012, 40(2):384-388. http://www.cnki.com.cn/Article/CJFDTOTAL-DZXU201202028.htmHAO G F, WANG Y R, ZHANG Z, et al.In-chip fault localization and self-repairing method for reconfigurable hardware[J].Chinese Journal of Electrics, 2012, 40(2):384-388(in Chinese). http://www.cnki.com.cn/Article/CJFDTOTAL-DZXU201202028.htm [7] ZHANG X, DRAGFFY G, PIPE A G, et al.Artificial innate immune system:An instant defence layer of embryonics[J].Lecture Notes in Computer Science, 2004, 3239(1):302-315. [8] CANHAM R O, TYRRELL A M.A hardware artificial immune system and embryonic array for fault tolerant systems[J].Genetic Programming and Evolvable Machines, 2003, 4(4):359-382. [9] CANHAM R O, TYRRELL A M.An embryonic array with improved efficiency and fault tolerance[C]//Proceedings 2003 NASA/DoD Conference on Evolvable Hardware.Piscataway, NJ:IEEE Press, 2003:265-272. [10] SAMIE M, DRAGFFY G, TYRRELL A M.Novel bio-inspired approach for fault-tolerant VLSI systems[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2013, 21(10):1878-1891. [11] BREMNER P, LIU Y, SAMIE M, et al.SABRE:A bio-inspired fault-tolerant electronic architecture[J].Bioinspiration & Biomimetics, 2013, 8(1):1-16. [12] UPEGUI A, THOMA Y, MORENO J M, et al.The perplexus bio-inspired reconfigurable circuit[C]//Proceedings 2007 NASA/ESA Conference on Adaptive Hardware and Systems.Piscataway, NJ:IEEE Press, 2007:600-605. [13] ABRAMOVICI M, EMMERT J M, STROUD C E.Roving STARs:An integrated approach to on-line testing, diagnosis, and fault tolerance for fpgas in adaptive computing systems[C]//Proceedings the 3rd NASA/DoD Workshop on Evolvable Hardware.Piscataway, NJ:IEEE Press, 2001:73-92. [14] BOLCHINI C, SALICE F, SCIUTO D.Designing self-checking FPGAs through error detection codes[C]//Proceedings 17th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems.Piscataway, NJ:IEEE Press, 2002:60-68. [15] STOTT E, SEDCOLE P, CHEUNG P Y K.Fault tolerant methods for reliability in FPGAs[C]//International Conference on Field Programmable Logic and Applications.Piscataway, NJ:IEEE Press, 2008:415-420. [16] BRAYTON R, MISHCHENKO A.ABC:An academic industrial-strength verification tool[J].Lecture Notes in Computer Science, 2010, 6174(1):24-40. [17] MISHCHENKO A, CHATTERJEE S, BRAYTON R.DAG-aware AIG rewriting:A fresh look at combinational logic synthesis[C]//Proceedings 2006 Design Automation Conference.Piscataway, NJ:IEEE Press, 2006:532-535. [18] LUU J, GOEDERS J, WAINBERG M, et al.VTR7.0:Next generation architecture and cad system for FPGAS[J].ACM Transactions on Reconfigurable Technology and Systems, 2014, 7(2):6. [19] MISHCHENKO A, CHATTERJEE S, BRAYTON R, et al.Improvements to combinational equivalence checking[C]//2006 IEEE/ACM International Conference on Computer Aided Design.Piscataway, NJ:IEEE Press, 2006:836-843. [20] MISHCHENKO A, CASE M, BRAYTON R, et al.Scalable and scalably-verifiable sequential synthesis[C]//2008 IEEE/ACM International Conference on Computer Aided Design.Piscataway, NJ:IEEE Press, 2008:234-241. [21] 朱赛, 蔡金燕, 孟亚峰.一种LUT型胚胎电子阵列的功能分化方法[J].电子学报, 2015, 43(12):2440-2448.ZHU S, CAI J Y, MENG Y F.A functional differentiation method for LUT-based embryonics array[J].Chinese Journal of Electrics, 2015, 43(12):2440-2448(in Chinese). -

下载:

下载: