An infrared small target detection network under various complex backgrounds realized on FPGA

-

摘要:

红外(IR)小目标检测算法具有检测率高、虚警率低、实时性好等优点在红外遥感领域有重要的应用价值。由于复杂背景下小目标对比度低和信噪比(SNR)低,传统红外小目标检测算法难以保证检测性能。在强鲁棒性的红外小目标检测网络(RISTDnet)基础上,面向更为多样的目标结构特征和更高的实时处理性能要求,提出一种增强型红外小目标检测网络(EISTDnet)与其基于现场可编程逻辑门阵列(FPGA)高性能并行处理的算法。EISTDnet构造了手工特征算法与卷积神经网络相结合的多尺度小目标特征提取框架,采用多级展开思路对卷积核尺寸进行归一化设计,并通过数据深度复用和多维循环并行展开有效提高推理阶段实时处理性能。实验结果表明:采用单片FPGA实现的EISTDnet能够快速实时检测复杂背景下不同大小、低信噪比的小目标,与现有5种算法相比在10−3低虚警率下平均检测率提升49.5%,与RISTDnet相比,在实时处理速度提高1.33倍的优势下,对低信噪比条状小目标检测率提升29.4%,所提算法具有更好的有效性和鲁棒性。

-

关键词:

- 卷积神经网络 /

- 红外小目标 /

- 目标检测 /

- 现场可编程逻辑门阵列 /

- 实时

Abstract:The infrared (IR) small target detection algorithm with high detection rate, low false alarm rate and good real-time performance has important application value in the field of IR remote sensing. Traditional IR small targets detection algorithms cannot guarantee the detection performance due to the low contrast and low signal-to-noise ratio (SNR) of small targets under various complex backgrounds. Based on robust infrared small target detection network (RISTDnet) proposed, for more diverse target structure characteristics and higher real-time processing performance requirements, an enhanced infrared small target detection network (EISTDnet) and its field programmable logic gate array (FPGA) based high-performance parallel processing method are proposed. In EISTDnet, a multi-scale small target feature extraction framework that combines manual feature methods and convolutional neural networks is constructed, the size of the convolution kernel is normalized by the idea of multi-level expansion, and real-time processing performance in the inference stage is effectively improved through deep data reuse and multi-dimensional loop parallel unfolding. Experimental results show that the EISTDnet realized on a single FPGA can quickly detect small targets with different sizes and low SNR in various complex backgrounds in real time. Compared with the existing 5 algorithms, the average detection rate is increased by 49.5% with a low false alarm rate of 10−3. Compared with RISTDnet, the real-time processing speed is increased by 1.33 times, and the detection rate of low SNR strip small targets is increased by 29.4%. EISTDnet has better effectiveness and robustness.

-

小目标检测在红外图像处理领域占有重要地位,特别是在遥感领域中具有较高的军民应用价值。而复杂背景下的低信噪比小目标检测是一项具有挑战性的任务,因为图像中的目标通常很小很弱并缺乏特定的形状、纹理和结构信息。

近几十年来,许多红外小目标检测算法被提出,算法主要包括单帧检测和多帧关联2个步骤。由于多帧关联往往是在单帧检测基础上进一步开展时域关联处理,因此,单帧检测算法对于复杂背景下弱小目标的检测能力更为关键。本文聚焦在红外小目标单帧检测算法的研究上,传统的单帧检测算法可分为两类:局部对比法(local contrast measure,LCM)和非局部自相关法(nonlocal autocorrelation measure,NAM)。

LCM主要是通过定义一种合理的局部对比度来抑制背景和增强小目标。Chen等[1]应用LCM来测量每个像素位置与其邻域之间的差异。Han等[2]进一步考虑中心子块的均值估计来改进LCM(improved local contrast measure,ILCM),并通过增加窗口的滑动步长提高算法效率。Wei等[3]提出一种基于多尺度图像块的对比度度量方法(multiscale patch-based contrast measure,MPCM),利用每个位置像素与其相邻区域的灰度比作为真实目标对比度的增强因子。类似的LCM还包括相对局部对比度度量(relative local contrast measure,RLCM)[4]和多尺度改进的LCM(multiscale modified local contrast measure,MLCM)[5]。Han等[6]联合比值和差值的局部对比度(ratio-difference joint local contrast measure,RDLCM)来增强小目标并抑制背景。

以红外块图像(infrared patch image,IPI)模型为代表的NAM利用目标的稀疏性和背景的低秩性将目标检测问题转化为最优化问题,然后通过求解目标函数来分离目标和背景[7]。IPI存在的2个明显缺点是检测结果中目标形态的过收缩和噪声残留,主要原因是采用核范数作为背景的低秩正则项。通过在IPI模型中引入更多的低秩矩阵恢复技术以获得更好的性能。Dai等[8]提出非负约束的红外块图像模型和加权的红外块图像张量模型(reweighted infrared patchtensor model,RIPT)[9],同时采用不同形式的紧秩对传统IPI模型低秩正则项替换来解决背景残留问题。此外,Zhang等[10]使用非凸秩逼近最小化联合范数,Zhou等[11]联合应用Schatten 1/2拟范数正则化和重加权稀疏增强来提高检测性能。

传统检测算法通常仅采用手工制作的特征,其性能取决于特征选取的有效性。深度学习可以从大量的训练数据中自动学习特征,更有助于描述数据中丰富而独特的信息。近年来一些基于深度学习的目标检测算法被提出,如Faster R-CNN[12]、YoloV2[13]、YoloV3[14]、SSD[15]等。这些算法对纹理明显的大目标具有很高的检测性能,但由于红外小目标纹理特征并不十分明显,现有深度学习算法难以适用。

针对现有检测算法的不足和应用对算法实时处理性能的需求,本文主要工作如下:①以文献[16]提出的强鲁棒型红外小目标检测网络(robust infrared small target detection network,RISTDnet)[16]为研究基础,面向更为丰富的目标结构特征和实时处理性能提升的需求,提出一种增强型红外小目标检测网络(enhanced infrared small target detection network,EISTDnet);②提出基于现场可编程逻辑门阵列(field programmable gate array,FPGA)平台的EISTDnet高性能实时并行处理优化与实现算法;③使用多幅测试图像对EISTDnet检测性能和实时处理性能进行了实验验证,并与其他检测算法进行了对比。

1. 检测算法原理

首先,利用EISTDnet计算目标似然图,似然图中的各像素值表征该像素属于小目标概率,然后,在目标似然图上设置阈值,进行阈值分割提取真实目标。

RISTDnet在复杂背景下对小目标已能够表现出较好的检测性能,但依然存在两方面不足:①通过对更多复杂场景下不同类型小目标进行测试,发现RISTDnet对部分呈现条状结构特征的低信噪比小目标检测能力偏弱,如图1所示的高分5号红外图像[17];②虽然能够在地面服务器中通过使用高性能GPU NVIDIA RTX2080Ti获得较好的RISTDnet处理性能,但在以空天飞行器为代表的算法应用场景中,受使用环境制约只能选用以FPGA为主的低功耗小体积嵌入式处理器,难以满足RISTDnet快速实时处理需求。针对上述问题,EISTDnet在研究中重点通过1.1节和1.2节介绍的两方面优化策略对网络结构开展重新设计。

1.1 强化多尺度特征提取

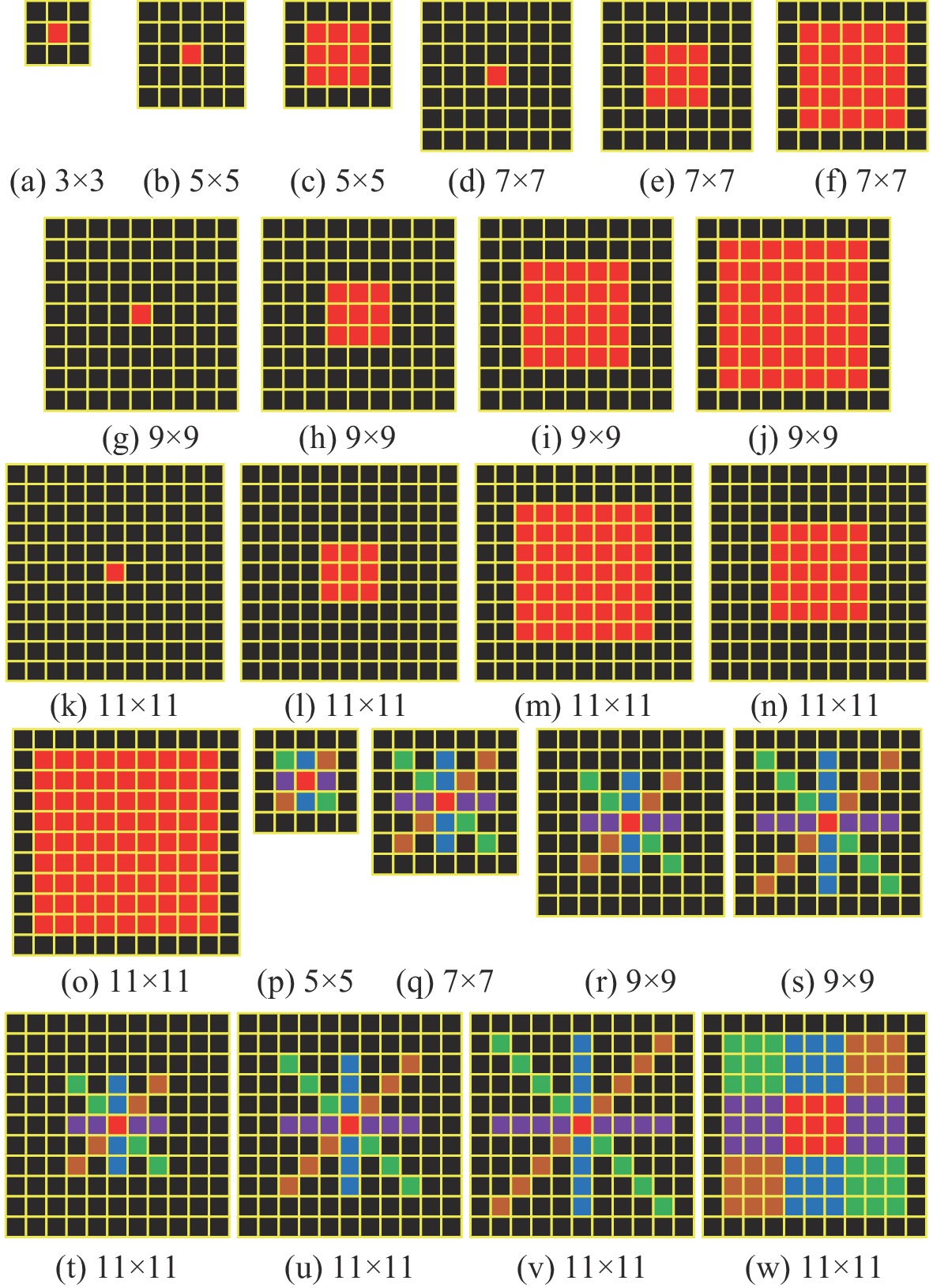

多尺度特征提取主要用于为复杂背景下的低信噪比小目标获得足够数量的特征图。RISTDnet定义了5种特征提取尺度:3×3、5×5、7×7、9×9和11×11,并通过15种定权卷积核生成15幅特征图,如图2(a)~图2(o)所示。这些定权卷积核在设计上均基于对图像中复杂背景和目标特性的研究而制定,以满足不同场景下有效特征提取。运算方式是以输入图像逐像素为中心,计算每个卷积核模板下邻域红色像素的平均值减去黑色像素的平均值,目的是提取小目标的对比度信息。

EISTDnet继承了RISTDnet特征提取定权卷积核对传统斑点状小目标提取能力,并针对复杂场景中更为丰富的条状小目标结构特征,新增8种定权卷积核,如图2(p)~图2(w)所示。这些卷积核的结果是以红色像素为中心,分别计算4种颜色条带的累加和,继而通过比较选出4个条带累加和中最大的那条,计算其与红色像素的平均值减去所有黑色像素的平均值,目的是增强不同方向下条状小目标对比度信息提取能力。

1.2 卷积网络轻量化

卷积网络主要采用深度学习算法用于对小目标深度特征进行提取。由于卷积运算为4层循环乘加运算,计算量庞大,因而EISTDnet在设计时充分考虑了应用中处理器性能约束,采用卷积核尺寸归一化、归一化(batch normalization,BN)层参数融合和特征映射层简化3种方法对卷积网络开展轻量化设计。

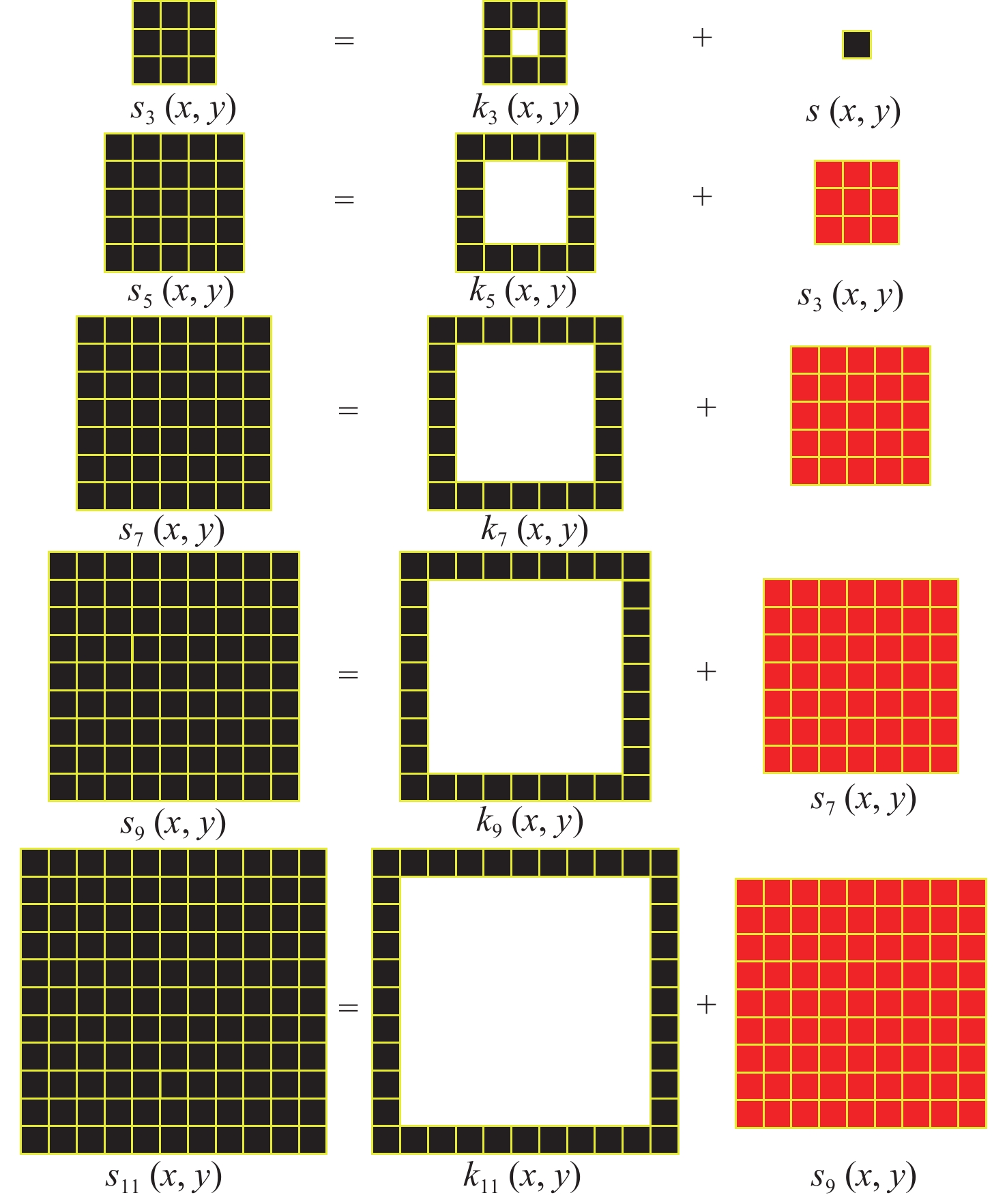

1) 卷积核尺寸归一化。RISTDnet卷积核包括11×11、7×7、5×5、3×3和1×1这5种尺寸规格,差异较大。这在对卷积层并行实时计算时,难以对卷积核并行展开。并且由于5种尺寸中除1×1外互相之间不能整除,因此并行展开时无法选择出一个适用于各层的最优卷积核展开尺度,这会造成部分计算资源的浪费。

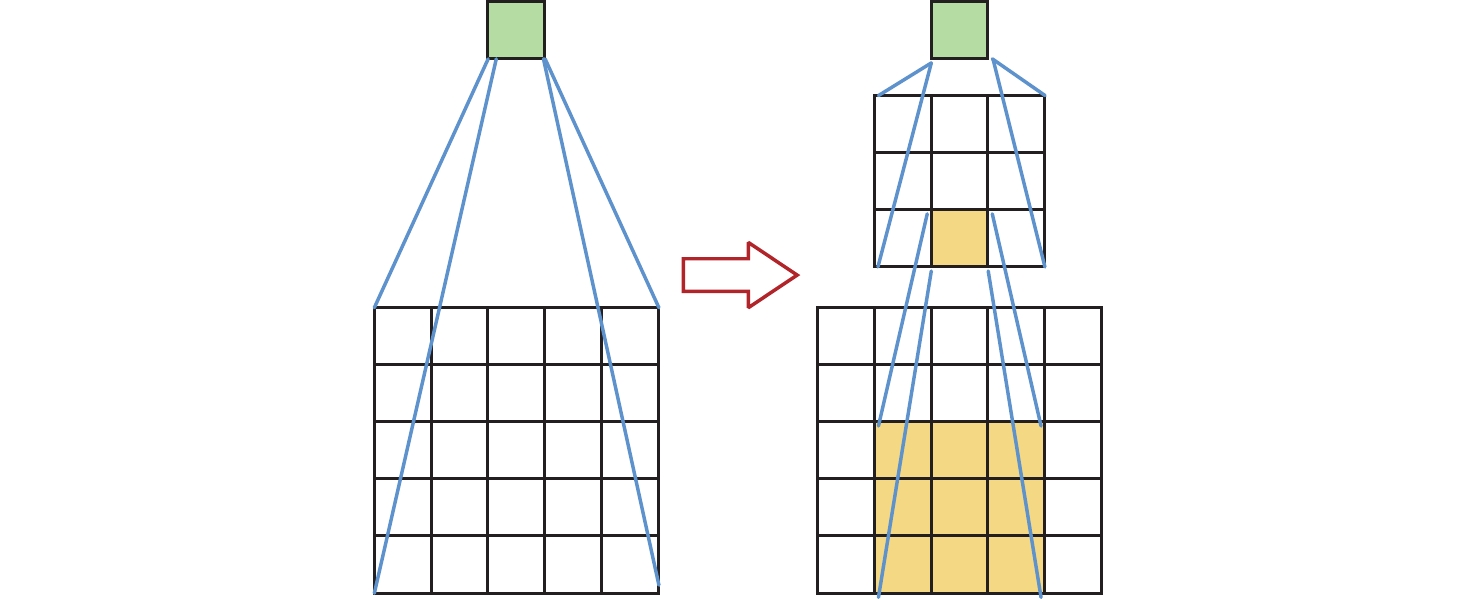

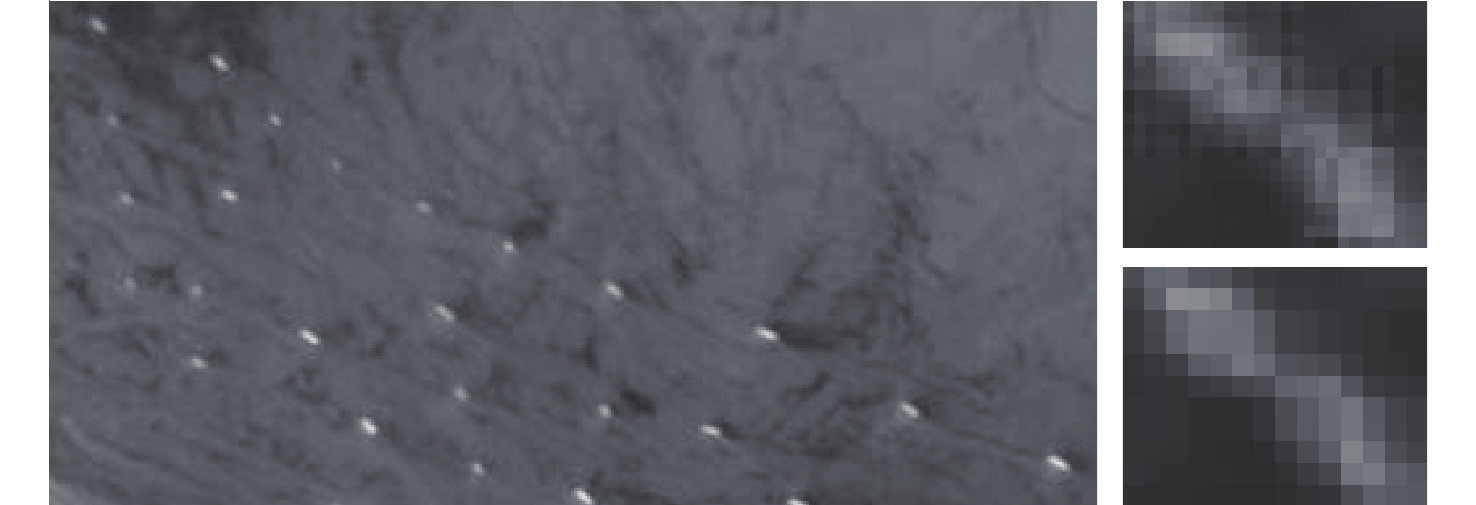

EISTDnet在设计中为提高实时处理架构并行展开能力,最大化利用处理资源,对较大卷积核采用多级小卷积核串联的方式予以优化,如图3所示。

由图3可以看出一个5×5的卷积核可以替换成2级3×3的卷积核,此时卷积权重个数由25降低至18,同理对于11×11和7×7卷积核可以分别替换成5级和3级3×3的卷积核,此时权重数量由121和49分别降低至45和27。优化算法在确保替换前后各卷积层感受野不变的情况下,大幅度降低了卷积核权重数,并将原有3×3尺度以上的卷积核归一化到3×3,有利于选择处理架构最优并行展开尺度,提高计算效率。

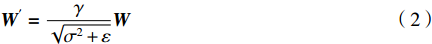

2) BN层参数融合。BN层主要是为在网络训练过程中解决梯度消失和梯度爆炸问题,同时提高泛化性能。BN层计算涉及到高精度乘加运算,因而在FPGA实现时需要消耗大量计算时间与参数存储资源。由于BN层在推理阶段参数已经完全固定,EISTDnet设计中对BN层采用训练后与卷积层参数融合的方式降低推理阶段计算资源开销。

设卷积计算为

Y=W⋅X+b (1) 式中:

Y 为卷积层输出;W 为卷积核参数;X 为卷积层输入;b 为偏置。BN层与卷积层融合后输出

Ybn 依然可依照式(1)进行卷积计算,仅需对W 和b 变量采用W′ 和b′ 进行参数更新:W′=γ√σ2+εW (2) b′=β+(b−μ)γ√σ2+ε (3) 式中:

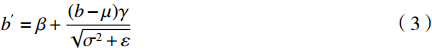

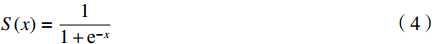

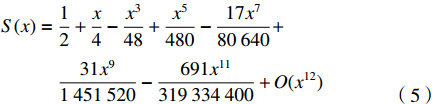

γ 为尺度因子;ε 为方差调整因子;β 为偏移因子;μ 和σ2 为每个通道的平均值与方差。这4个变量均为训练结束后BN层静态参数。3) 特征映射层简化。RISTDnet特征映射层采用Sigmoid函数将特征提取结果分别映射到目标和背景似然图。以x为变量Sigmoid函数定义为

S(x)=11+e−x (4) Sigmoid函数具有单增性质,可将变量映射到[0,1]内,从而获得百分比表示的概率似然值。在网络训练阶段通过Sigmoid函数获得概率似然值有利于计算损失函数,但其推理阶段FPGA处理中通常需采用级数展开算法进行运算,如式(5)所示,式中O(x12)为可忽略的极小项。这些高次方级数展开计算会消耗FPGA大量乘加运算资源。

S(x)=12+x4−x348+x5480−17x780640+31x91451520−691x11319334400+O(x12) (5) 考虑到映射后数值在实时处理中仅用于阈值分割,因而在EISTDnet设计中将推理阶段特征映射函数简化为

S(x)=x ,相对Sigmoid函数运算开销降低明显,仅需要通过调整阈值分割取值即可获得同等目标提取精度,不会影响网络检测性能。1.3 EISTDnet网络结构

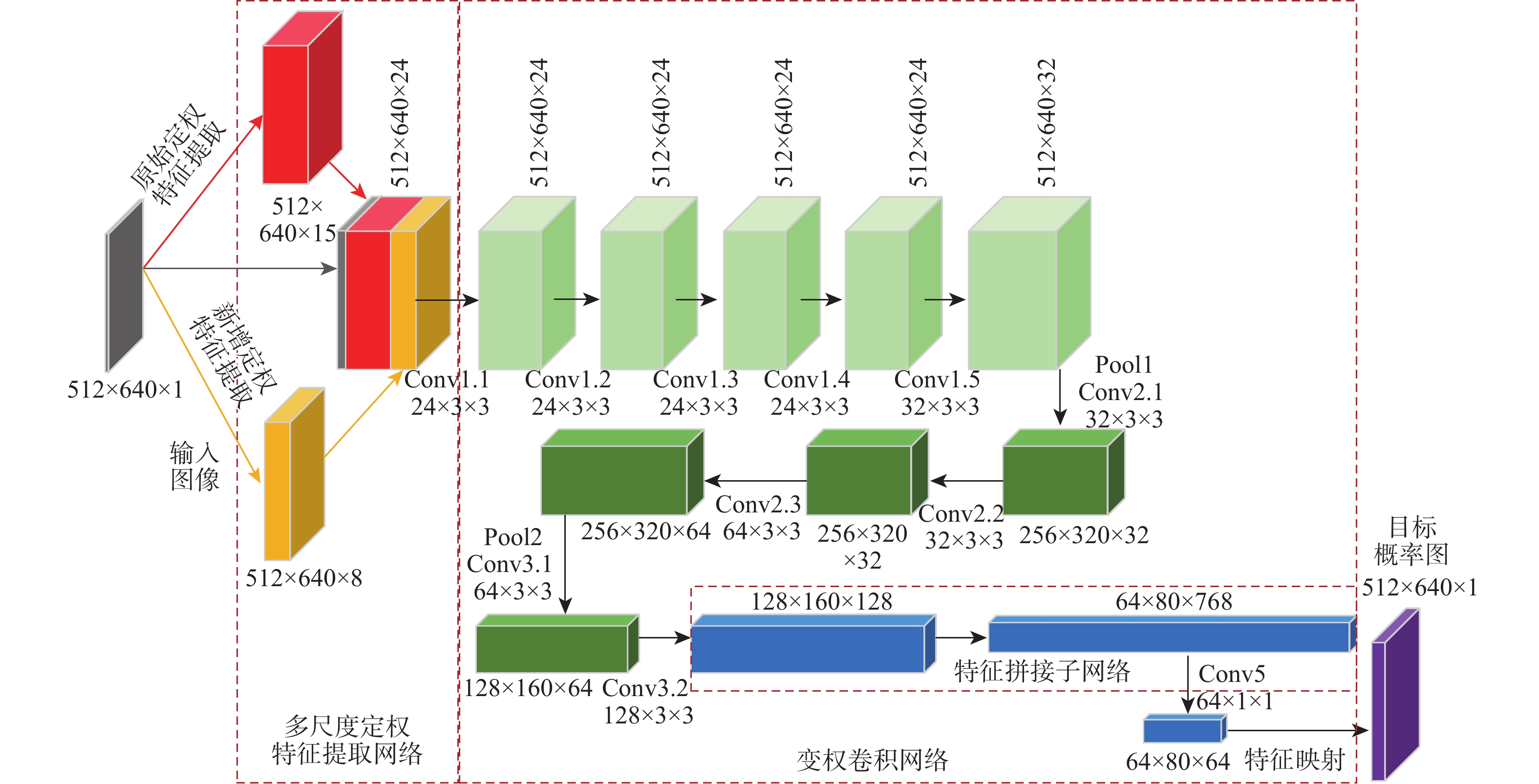

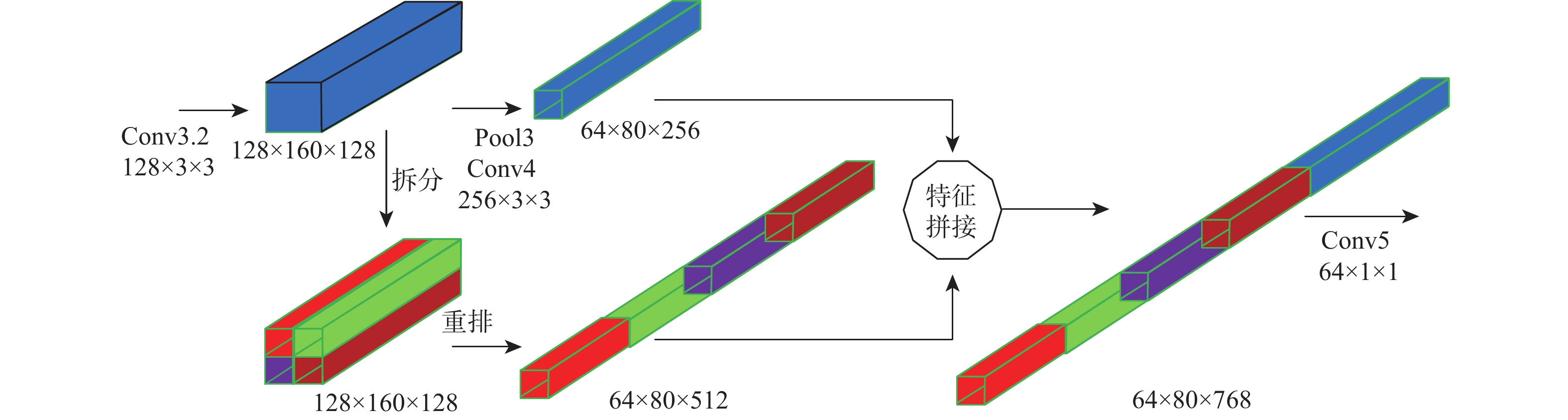

采用强化多尺度特征提取和卷积网络轻量化两方面优化策略后,EISTDnet网络结构如图4所示,主要由多尺度定权特征提取网络和变权卷积网络两部分组成。

多尺度定权特征提取网络主要用于提取手工制作的多尺度特征,其中,红色方框示意的15种特征提取图采用继承RISTDnet的原始定权特征卷积核提取,黄色方框示意的8种特征提取图为EISTDnet新增的特征卷积核提取,提取后将原图与特征图串联作为变权卷积网络输入。变权卷积网络通过采用自学习训练后参数进一步对目标深度特征进行提取。

变权卷积网络中包含一个特征拼接子网络,采用Passthrough层结构设计。如图5所示,特征连接子网络在对高分辨率特征图进行分割和重新排列后,将结果与卷积后低分辨率特征图连接起来,形成多尺度特征图,更有利于检测不同大小的小目标。

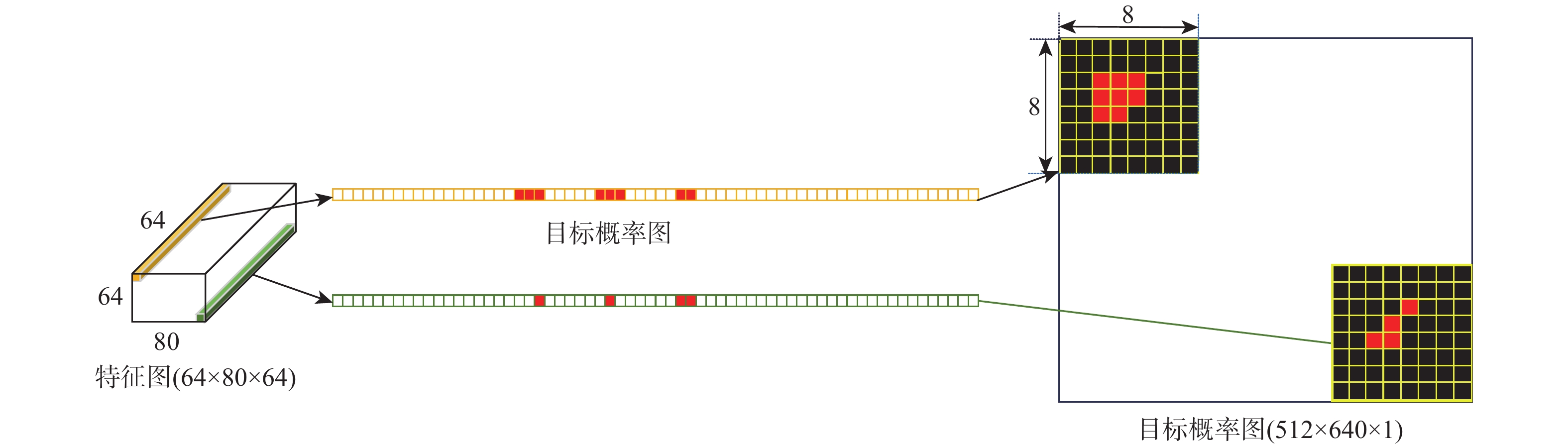

变权卷积网络中的特征映射层采用简化设计方法,在推理阶段仅需要将输入的特征图进行通道展开重新组织即可生成目标似然图用于后续阈值分割,如图6所示。

从网络结构可以看出EISTDnet是一个多尺度手工制作特征和深度自学习特征融合的小目标检测框架,其网络参数如表1所示。其中各卷积层后均跟有ReLU层,篇幅考虑不予表中列出。

表 1 EISTDnet网络参数Table 1. EISTDnet network parameters层编号 卷积核

数量卷积核

尺寸/步长输出特征图

尺寸特征提取 512×640 Conv1.1 24 3×3/1 512×640 Conv1.2 24 3×3/1 512×640 Conv1.3 24 3×3/1 512×640 Conv1.4 24 3×3/1 512×640 Conv1.5 32 3×3/1 512×640 Pool1 2×2/2 256×320 Conv2.1 32 3×3/1 256×320 Conv2.2 32 3×3/1 256×320 Conv2.3 64 3×3/1 256×320 Pool2 2×2/2 128×160 Conv3.1 64 3×3/1 128×160 Conv3.2 128 3×3/1 128×160 Pool3 2×2/2 64×80 Conv4 256 3×3/1 64×80 Conv5 64 3×3/1 64×80 表2给出了EISTDnet相对RISTDnet在各项优化策略应用前后运算操作数变化。可以直观看出由于新增了8种多尺度特征提取,EISTDnet运算操作数相对RISTDnet增加了29.23%。但通过应用3种网络轻量化优化方法,EISTDnet运算操作数降低至RISTDnet的48.46%,有效削减了推理阶段实时处理计算资源需求。

表 2 EISTDnet与RISTDnet运算操作数比对Table 2. Comparison of operands between EISTDnet and RISTDnet网络改进阶段 运算操作数 RISTDnet 69999411200 EISTDnet强化多尺度特征 90460323840 EISTDnet卷积网络轻量化 33919795200 2. FPGA处理优化与实现

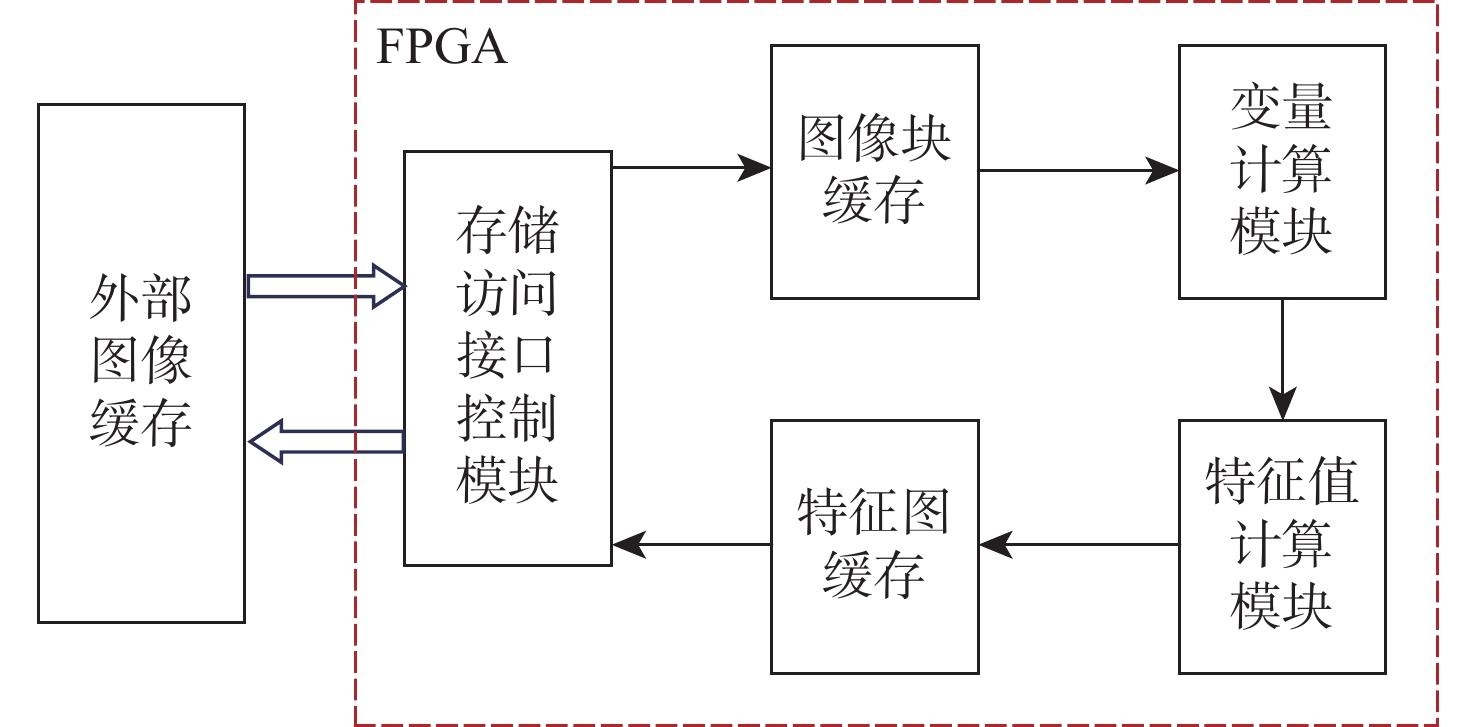

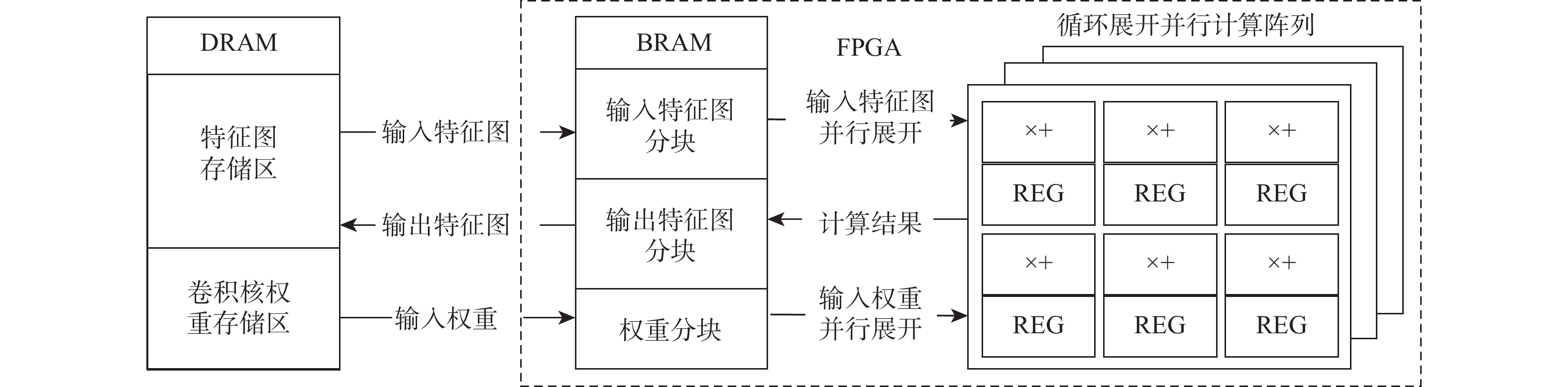

EISTDnet网络结构主要由多尺度定权特征提取网络和变权卷积网络两部分组成。其中变权卷积网络中卷积操作采用常规卷积运算,而多尺度定权特征提取网络由于新加入8种基于四向特征点比较的特征提取卷积核,其计算过程无法简单转化为常规卷积运算。因此,在顶层设计上EISTDnet采用独立模块分别实现多尺度定权特征提取网络和变权卷积网络实时处理。

与CPU、DSP等嵌入式处理器不同,FPGA可以针对算法内不同处理单元计算需求与特点量身定制处理电路,并采用数据复用、并行处理与流水处理等设计算法构建高性能处理架构。EISTDnet实现中有效运用了这些设计算法。

2.1 多尺度特征提取网络优化与实现

多尺度定权特征提取网络中不同特征提取卷积核之间存在数据深度复用关系,如图7所示。

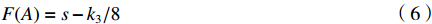

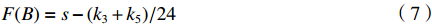

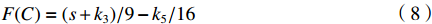

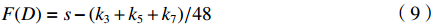

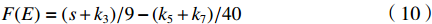

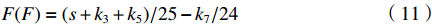

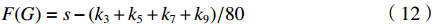

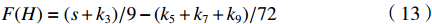

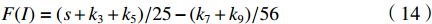

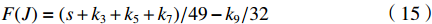

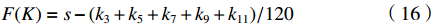

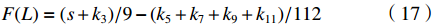

对于输入图像中坐标为

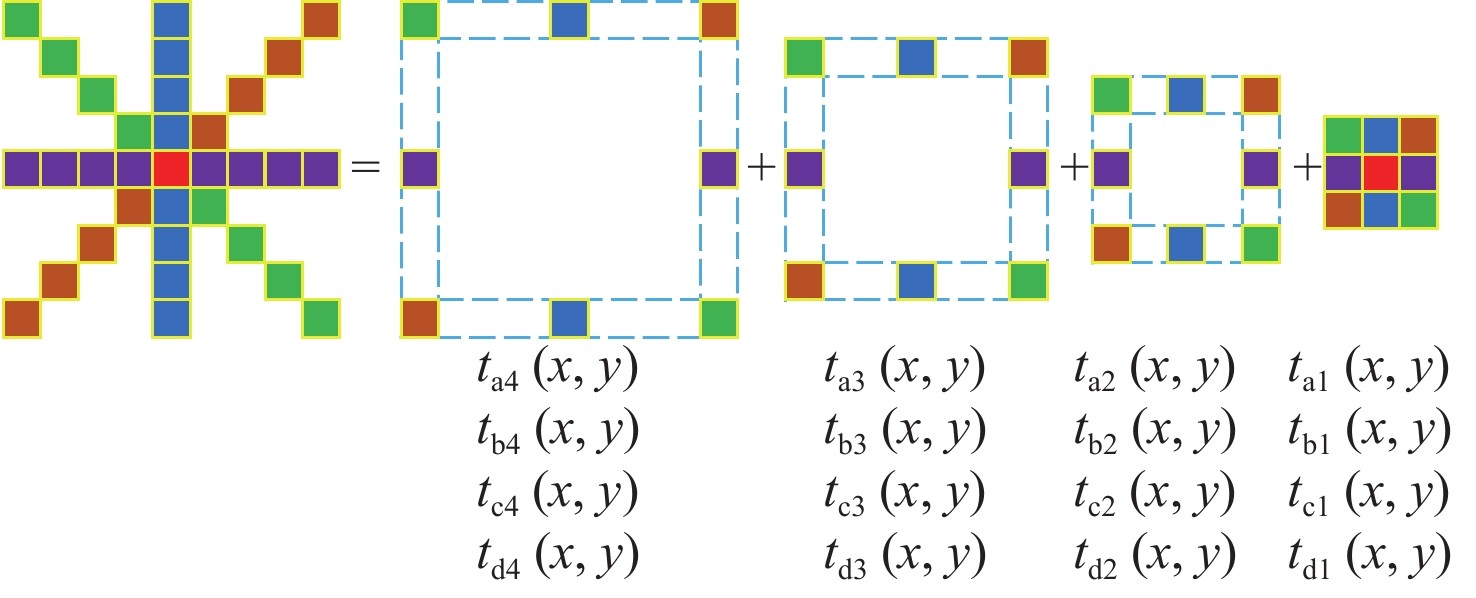

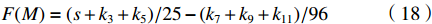

(x,y) 的像素,设其灰度值为s ,则由图7可以直观看出,只要再计算以该像素为中心的k3 、k5 、k7 、k9 和k11 这5个不同尺度框体和变量,即可获得图2(a)~图2(o)15种不同特征提取卷积核对应特征值,对应关系如式(6)~式(20)所示。F(A) 代表图2(a)卷积核特征提取值,其余标号以此类推:F(A)=s−k3/8 (6) F(B)=s−(k3+k5)/24 (7) F(C)=(s+k3)/9−k5/16 (8) F(D)=s−(k3+k5+k7)/48 (9) F(E)=(s+k3)/9−(k5+k7)/40 (10) F(F)=(s+k3+k5)/25−k7/24 (11) F(G)=s−(k3+k5+k7+k9)/80 (12) F(H)=(s+k3)/9−(k5+k7+k9)/72 (13) F(I)=(s+k3+k5)/25−(k7+k9)/56 (14) F(J)=(s+k3+k5+k7)/49−k9/32 (15) F(K)=s−(k3+k5+k7+k9+k11)/120 (16) F(L)=(s+k3)/9−(k5+k7+k9+k11)/112 (17) F(M)=(s+k3+k5)/25−(k7+k9+k11)/96 (18) F(N)=(s+k3+k5+k7)/49−(k9+k11)/72 (19) F(O)=(s+k3+k5+k7+k9)/81−k11/40 (20) 同理对于EISTDnet新增定权特征提取卷积核,也存在如图8所示复用关系。

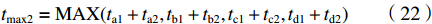

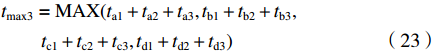

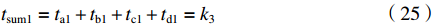

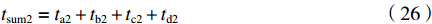

对于输入图像中坐标为

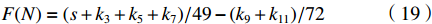

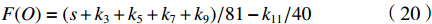

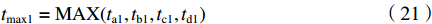

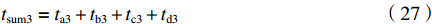

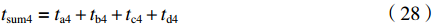

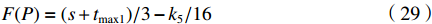

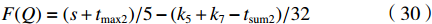

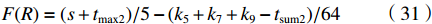

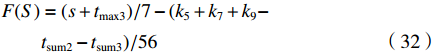

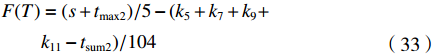

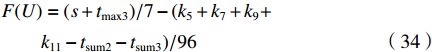

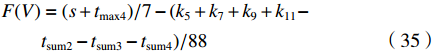

(x,y) 的像素,设ta1/2/3/4 分别代表以其为中心,纵向距离为1像素、 2像素、3像素和4像素的2点和变量,tb1/2/3/4 、tc1/2/3/4 和td1/2/3/4 分别代表以其为中心,其他3个方向距离为2点和变量。设tmax1/2/3/4 和tsum1/2/3/4 分别为四向2点和的最大值变量与四向2点和的累加和变量,如式(21)~式(28)所示,MAX为取最大值运算符。tmax1=MAX(ta1,tb1,tc1,td1) (21) tmax2=MAX(ta1+ta2,tb1+tb2,tc1+tc2,td1+td2) (22) tmax3=MAX(ta1+ta2+ta3,tb1+tb2+tb3,tc1+tc2+tc3,td1+td2+td3) (23) tmax4=MAX(ta1+ta2+ta3+ta4,tb1+tb2+tb3+tb4,tc1+tc2+tc3+tc4,td1+td2+td3+td4) (24) tsum1=ta1+tb1+tc1+td1=k3 (25) tsum2=ta2+tb2+tc2+td2 (26) tsum3=ta3+tb3+tc3+td3 (27) tsum4=ta4+tb4+tc4+td4 (28) 则对于图2(p)~图2(w)中8种新增特征提取卷积核,对应特征值关系如式(29)~式(35)所示。

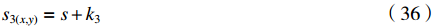

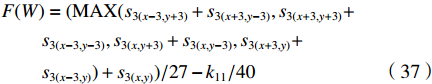

F(P)=(s+tmax1)/3−k5/16 (29) F(Q)=(s+tmax2)/5−(k5+k7−tsum2)/32 (30) F(R)=(s+tmax2)/5−(k5+k7+k9−tsum2)/64 (31) F(S)=(s+tmax3)/7−(k5+k7+k9−tsum2−tsum3)/56 (32) F(T)=(s+tmax2)/5−(k5+k7+k9+k11−tsum2)/104 (33) F(U)=(s+tmax3)/7−(k5+k7+k9+k11−tsum2−tsum3)/96 (34) F(V)=(s+tmax4)/7−(k5+k7+k9+k11−tsum2−tsum3−tsum4)/88 (35) 对于

F(W) 则需要通过记录坐标(x,y) 相邻点变量予以计算,设s3(x,y) 为坐标(x,y) 邻域3×3区域累加和,则可通过如式(36)~式(37)所示计算F(W) 。s3(x,y)=s+k3 (36) F(W)=(MAX(s3(x−3,y+3)+s3(x+3,y−3),s3(x+3,y+3)+s3(x−3,y−3),s3(x,y+3)+s3(x,y−3),s3(x+3,y)+s3(x−3,y))+s3(x,y))/27−k11/40 (37) 从式(6)~式(37)推导可得出,由于计算时存在大量的数据复用,在处理时仅需要对原图各像素通过加法简单计算出

k3 、k5 、k7 、k9 、k11 和tsum2/3/4 这8个变量,继而通过最大值比较运算获得tmax1/2/3/4 这4个变量,即可进一步通过简单线性计算获得23幅特征图对应特征点,循环全图所有像素即可获得23幅特征图。由于所提算法采用分块循环计算这一设计思路,因而并不受固定图像分辨率大小制约,可满足不同分辨率图像特征提取需求。与优化前卷积形式计算算法相比,得益于不同模板之间的耦合性和数据深度复用策略,优化后可大幅度降低图像读取次数与运算操作数,提高处理速率的同时降低FPGA内部资源占用,如表3所示(以640×512输入图像为例)。

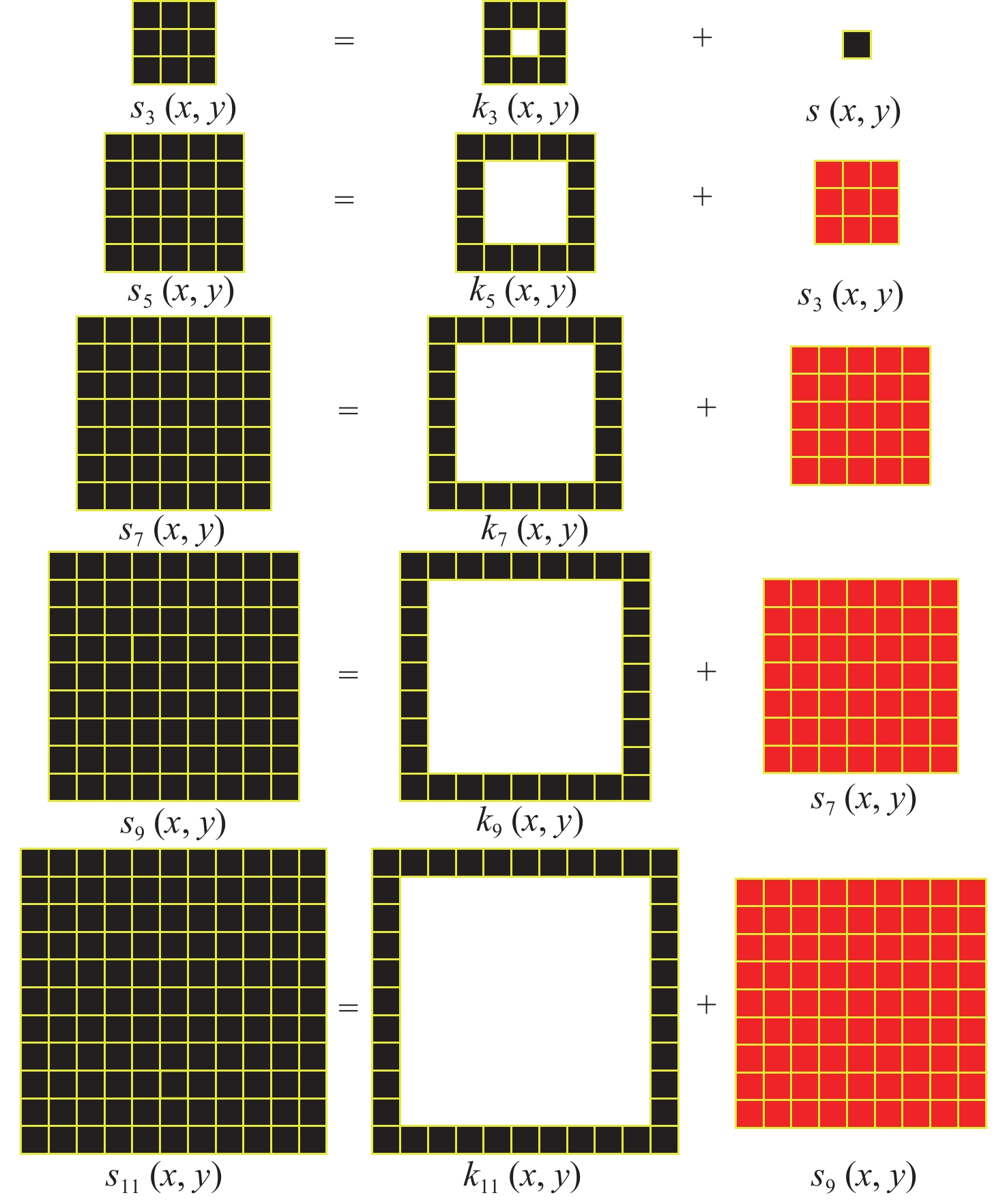

表 3 图像读取与运算操作比对Table 3. Image reading and operation comparison算法 像素读取次数 运算操作数 优化前 607846400 629473280 优化后 39649280 97648640 降低比例/% 6.52 15.51 基于本节优化方式,特征提取模块FPGA实现框图如图9所示,其中变量计算模块和特征值计算模块均采用并行计算方式对读出图像点进行快速处理,同时图像块缓存采用乒乓设计以保证整体运算单元处于高效流水工作状态。

2.2 变权卷积网络优化与实现

EISTDnet变权卷积网络中超过90%的操作涉及到卷积,因此,基于FPGA的实时处理设计侧重于卷积并行计算的优化。为实现变权卷积网络高性能快速处理,需重点考虑以下3点优化目标:

1) 在FPGA内计算资源允许条件下尽可能构建大规模并行流水计算架构,减少计算单元等待周期,降低计算延时,提高处理性能;

2) 基于有限片内缓存加强数据复用设计,尽可能降低外部缓存访问频次,以降低外部存储器吞吐和规模需求,节约硬件成本和功耗开销;

3) 充分利用分布式寄存器提高FPGA布局布线后工作频率,进一步提高系统整体处理性能。

2.2.1 多维循环并行展开优化

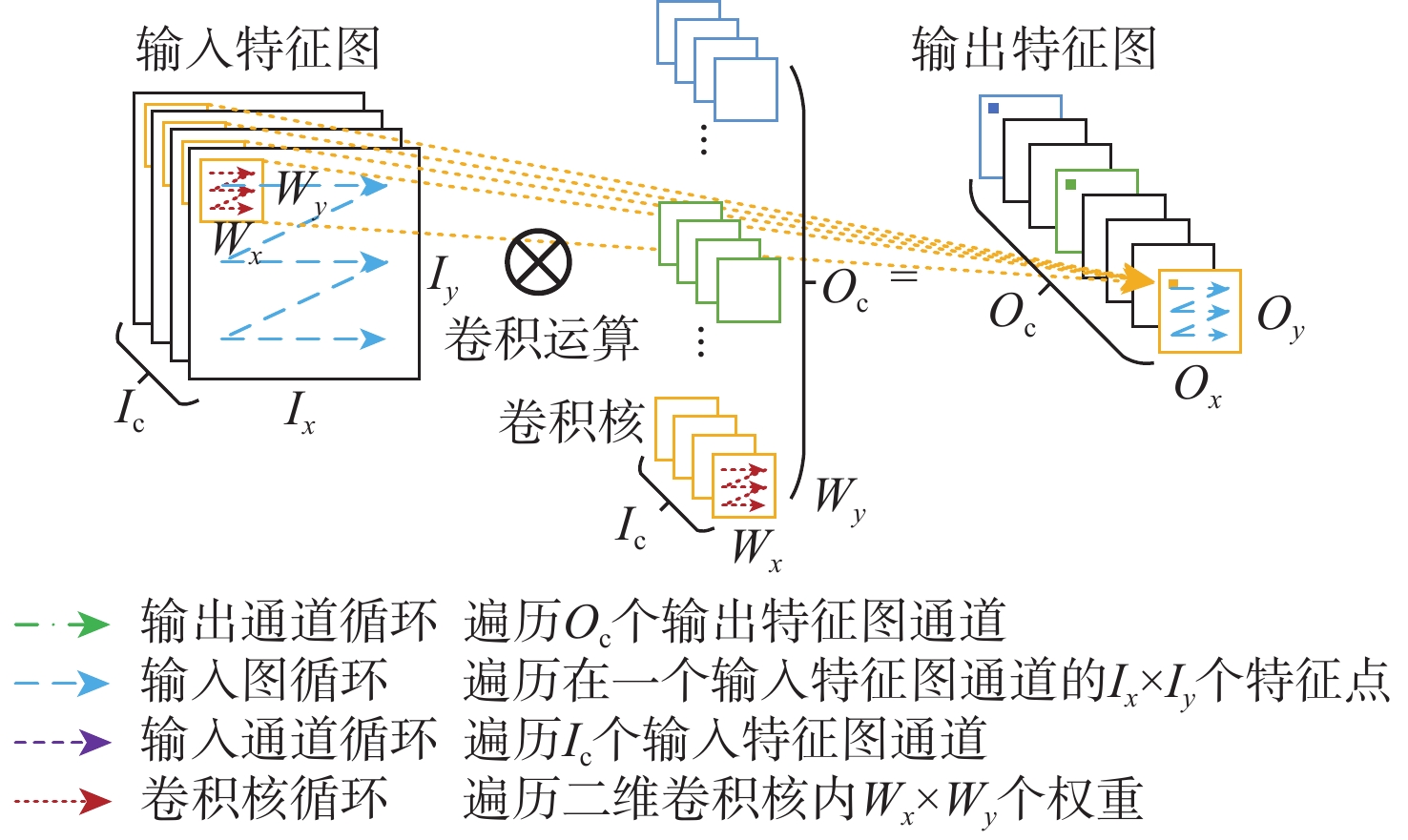

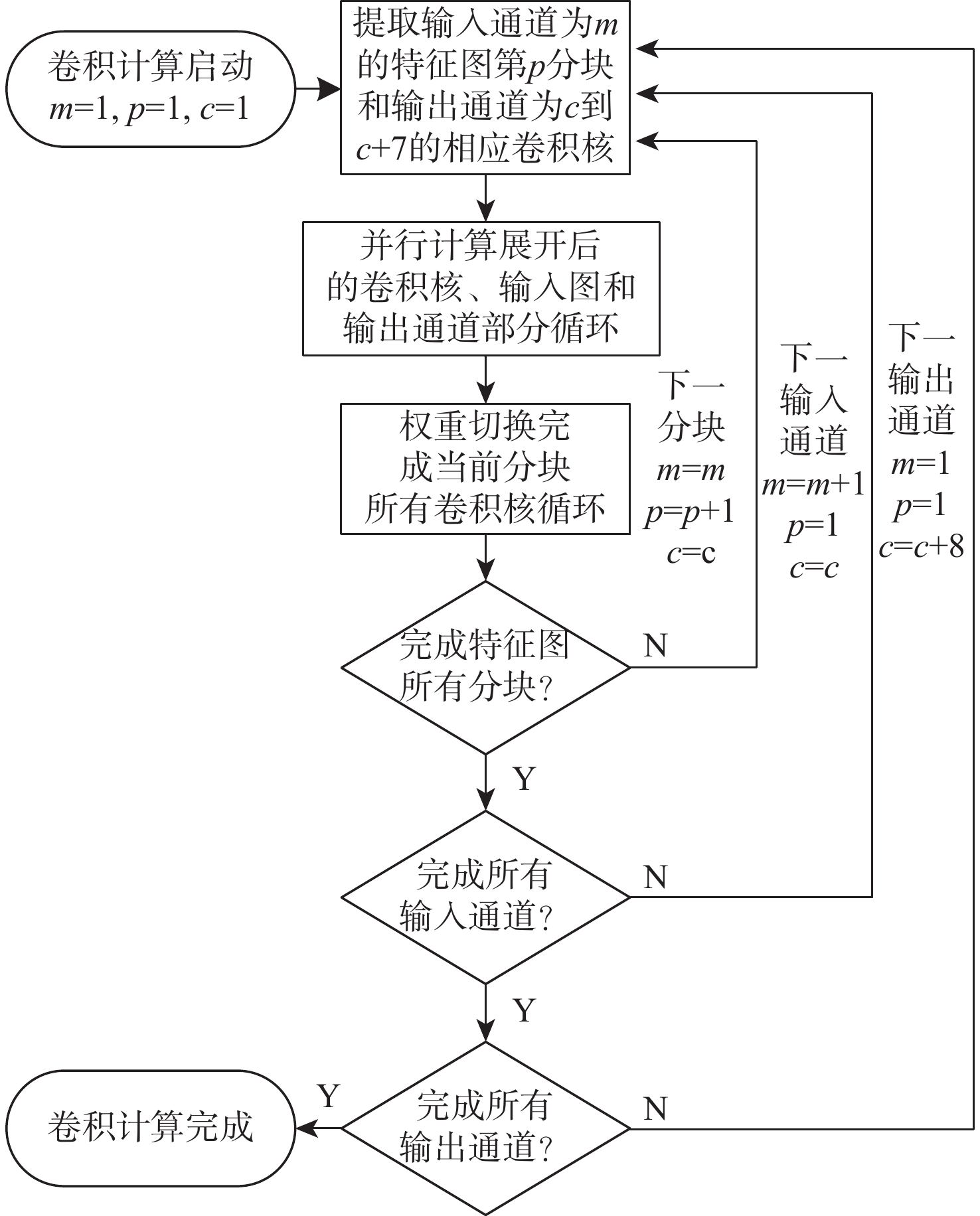

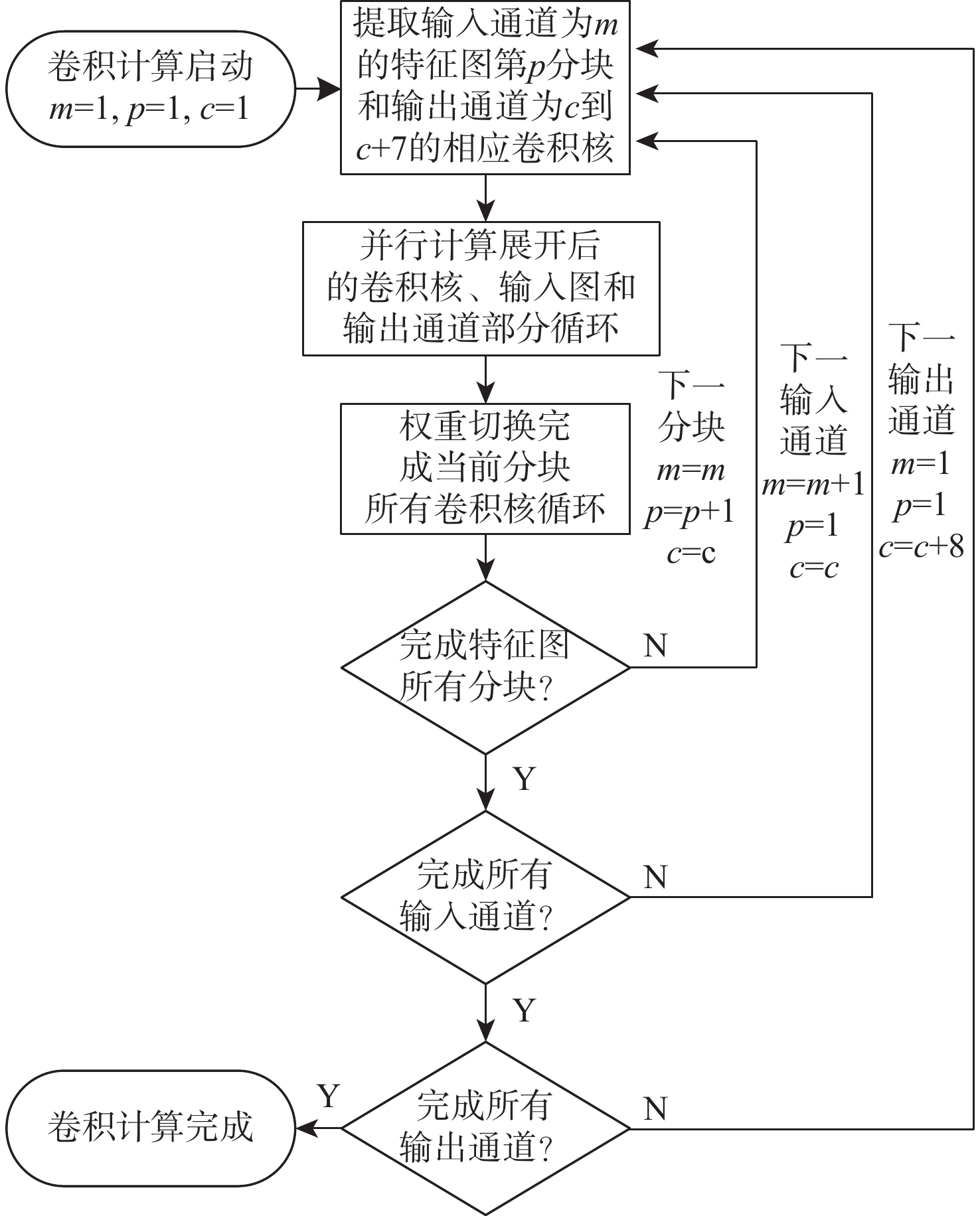

卷积网络中的卷积运算操作由4层循环组成,如图10所示。这些循环沿着卷积核和特征图滑动从而产生丰富的优化设计空间,其中最为关键的是循环并行展开的层次、维度和规模。

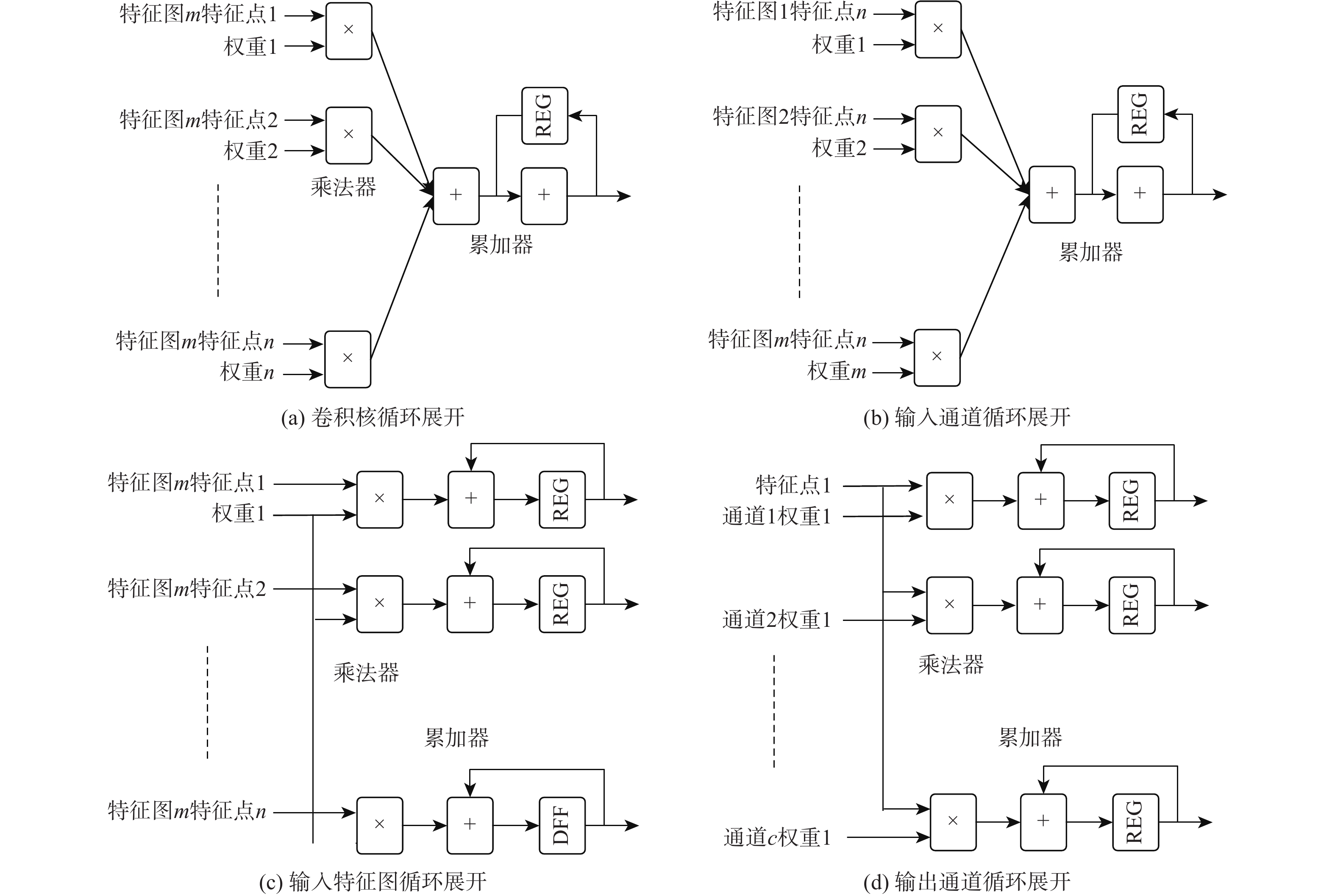

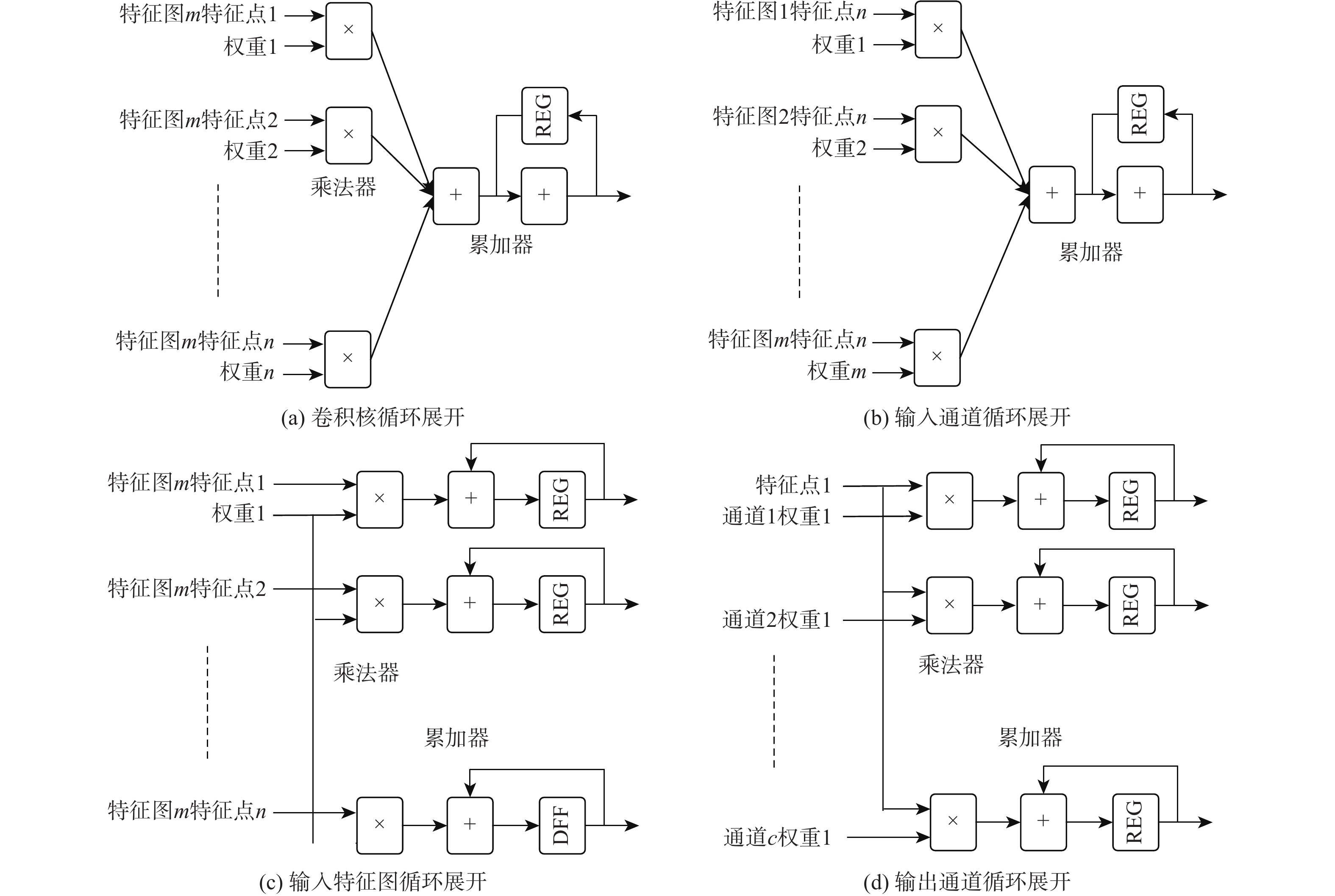

循环展开的维度与方式决定了卷积计算中不同的并行化设计,继而会影响处理架构优化设计中数据复用和存储访问方式。4层循环各自一维展开如图11所示。

从图11中可以直观看出,卷积核循环和输入通道循环展开有助于快速生成输出特征点,节省处理中间结果缓存,但展开并行计算时不同乘法器所需的输入特征点和权重均不同,复用度较低,对输入特征图和权重缓存访问吞吐量要求较高;输入特征图和输出通道展开分别充分复用了权重和特征点,但并行计算中间结果分属不同输出特征值,需要较大输出中间结果缓存深度。

并行展开尺度对不同卷积层的契合度直接影响整体并行架构运算效率,即各维度展开尺度应为不同层相关维度的公因数,否则会在处理过程中无法充分利用展开后的并行度,例如对于EISTDnet输出通道展开时,若将并行尺度设为24,则在处理Conv1.1层时利用率为100%,但在处理Conv2.1层时利用率会降低为75%。因而仅采用一维循环展开时往往会受限于公因数大小难以构建高利用率大规模并行展开架构,多维展开能够有效解决该难题。

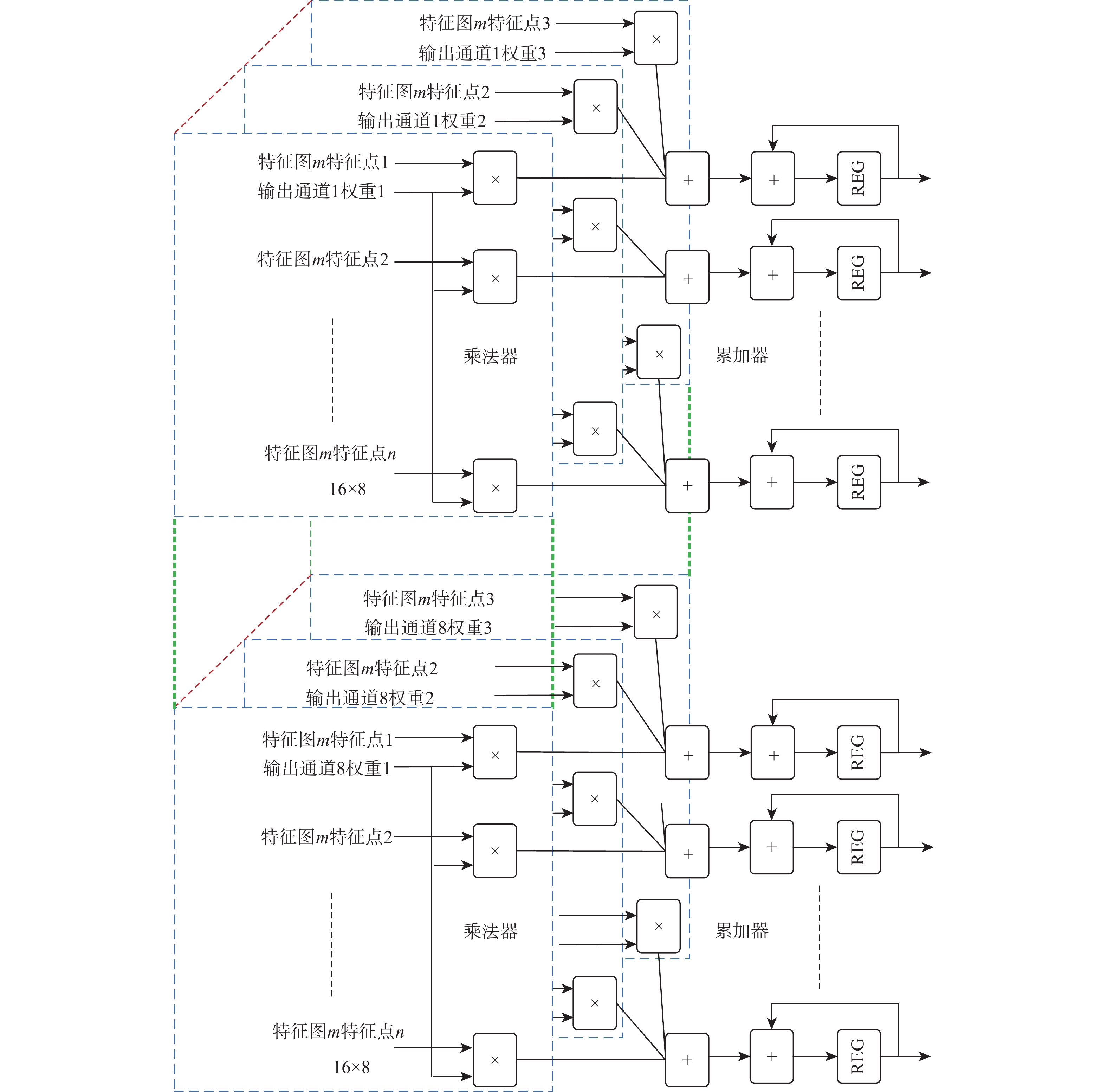

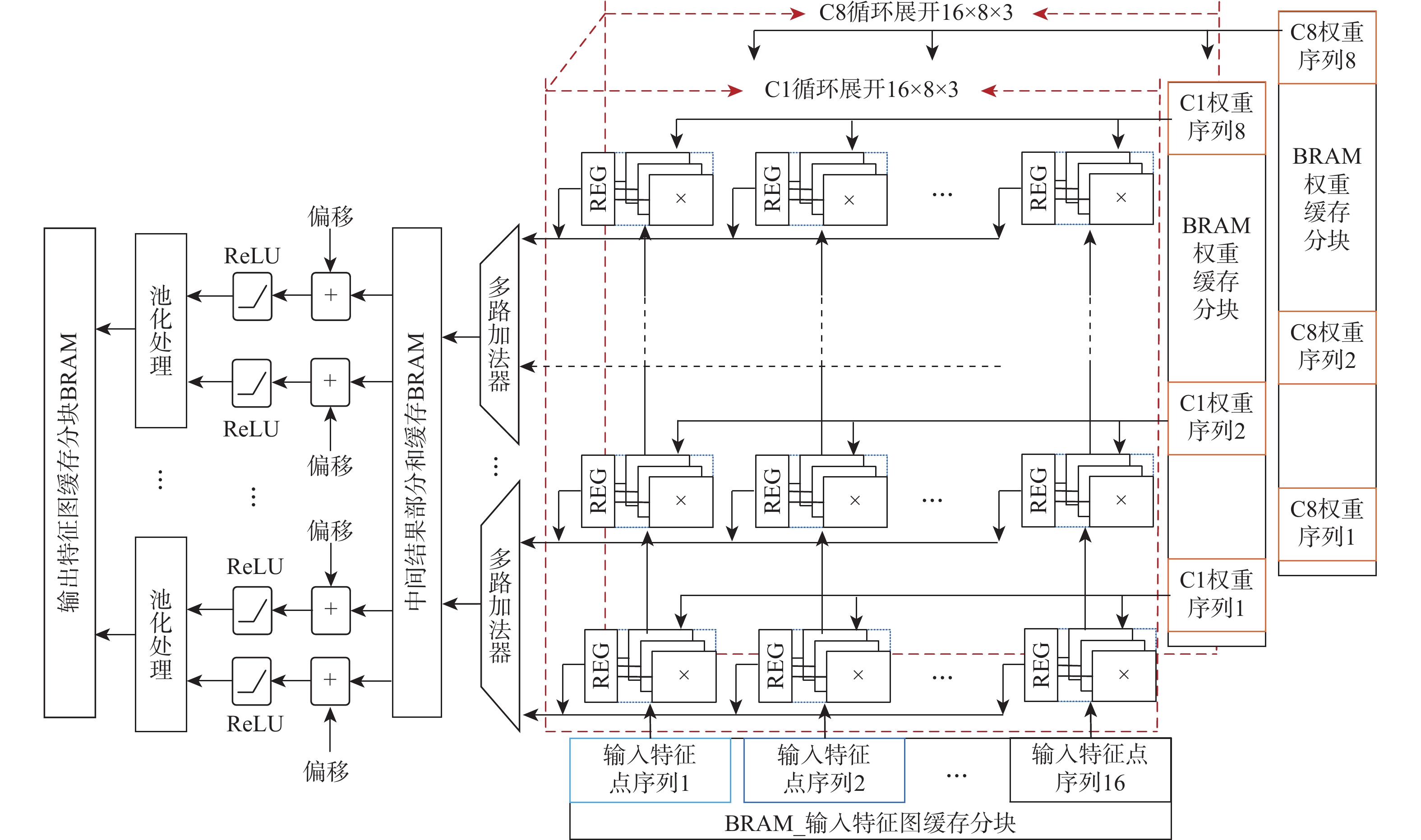

EISTDnet在网络结构设计时运用了卷积核尺寸归一化设计算法,除最后一层外其余各层卷积核均为3×3。同时输入和输出通道数各层最大公因数均为8,输入特征图各层最大公因数为64×80。受限于FPGA片内乘法器数量,为最大化并行度和尽可能提升数据复用率,并平衡不同展开维度对缓存带宽和深度影响,EISTDnet适合采用卷积核、输入特征图和输出通道三维循环展开,如图12所示。此时卷积核循环并行展开度为3,输入特征图并行展开度为16×8,输出通道并行展开度为8,整体并行度为3072。

2.2.2 多级缓存与循环计算顺序优化

变权卷积网络在FPGA实现中涉及多级缓存单元,从类型上分主要包含片外动态随机存储器(dynamic RAM,DRAM)、块缓存(block RAM,BRAM)和寄存器(register,REG)3种。如图13所示,REG在FPGA片内,与计算资源耦合紧密,使用灵活但容量最小;BRAM同属片内资源,并为双口RAM形式,吞吐能力强,但使用规模与扇出过大时会影响布线后时序,需在REG配合下使用;DRAM具有较大容量,但吞吐能力受输入输出(input output,IO)限制,延迟相对较大,过度使用也会直接加剧硬件成本和功耗开销。

受BRAM和REG数量限制FPGA内无法存储完整的特征图,每层卷积计算时需将待处理的输入特征图划分为多个块依次从DRAM中读出。结合循环展开机制,通过优化卷积循环计算顺序和分块大小,可以有效增加片内缓冲区数据的重复使用、减少片上缓存需求并降低外部DRAM访问频次,避免因DRAM访问带来的长延迟和高功耗。

在循环计算顺序选择中为尽快生成可直接存入外部DRAM的输出特征值,节省片内输出特征值中间结果缓存,输出通道循环除已展开的部分外其余应放在最后进行。此外,由于输入特征图尺寸相对卷积核较大,并且循环展开中输入特征图展开尺度也大于卷积核展开尺度,为充分复用当前展开的特征图,降低片内缓存吞吐压力,卷积核循环应首先完成,再完成输入特征图循环。此时输入特征图分块可按输入通道依次缓存,卷积核片内缓存则需要从外部缓存搬入当前分块对应的8个输出通道全部权重,从而最大化片内数据复用,降低DRAM吞吐压力。如图14所示变权卷积网络循环最优计算顺序。

2.2.3 高性能计算架构

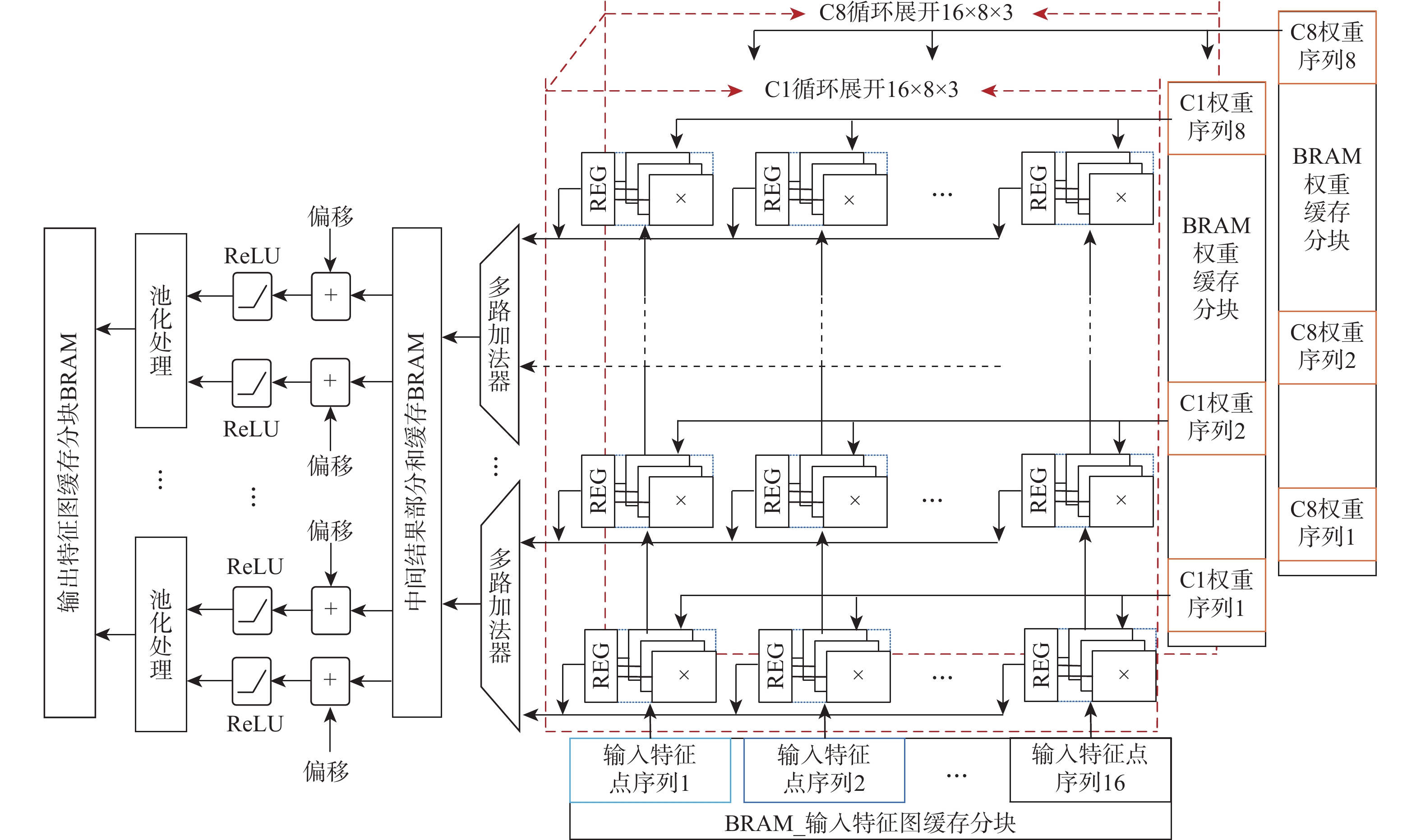

依据多维循环并行展开、循环计算顺序和多级缓存优化设计结果,EISTDnet变权卷积网络在实现中构建了以8个16×8×3并行计算矩阵为主的实时高性能并行处理架构,如图15所示,其中C1~C8对应8个输出通道循环展开。每个矩阵中包含16×8个计算单元,每个计算单元中包含的3个乘法器用于对卷积核循环展开并行计算。

考虑到卷积核权重需要从缓存中同时为多个计算单元更新,因而将权重队列设为8×8,每个权重队列仅负责更新当前矩阵横排的8个计算单元,以控制每个权重队列扇出。而对于输入特征图队列,则采用依次传递的方式对不同矩阵进行更新,更新后的特征点在计算单元内利用分布式寄存器进行缓存,同时控制了输入特征点队列扇出和队列数量,有效抑制当并行计算单元规模过大时由扇出引入的时序问题,以进一步优化FPGA布局布线后时钟频率,提高处理性能。

此外,对于EISTDnet变权卷积网络处理中特征拼接需求,在设计中采用外部缓存地址动态管理的方式对数据进行虚拟拼接,即在相关层特征图BRAM分块向DRAM存储时依据拼接需求动态调整读写地址,避免拼接数据搬移对处理架构带来的额外负担。

3. 实验结果与分析

为验证EISTDnet及FPGA实现性能,构建了训练和测试实验数据集,并以FPGA处理板为核心搭建了一整套实验与测试平台。

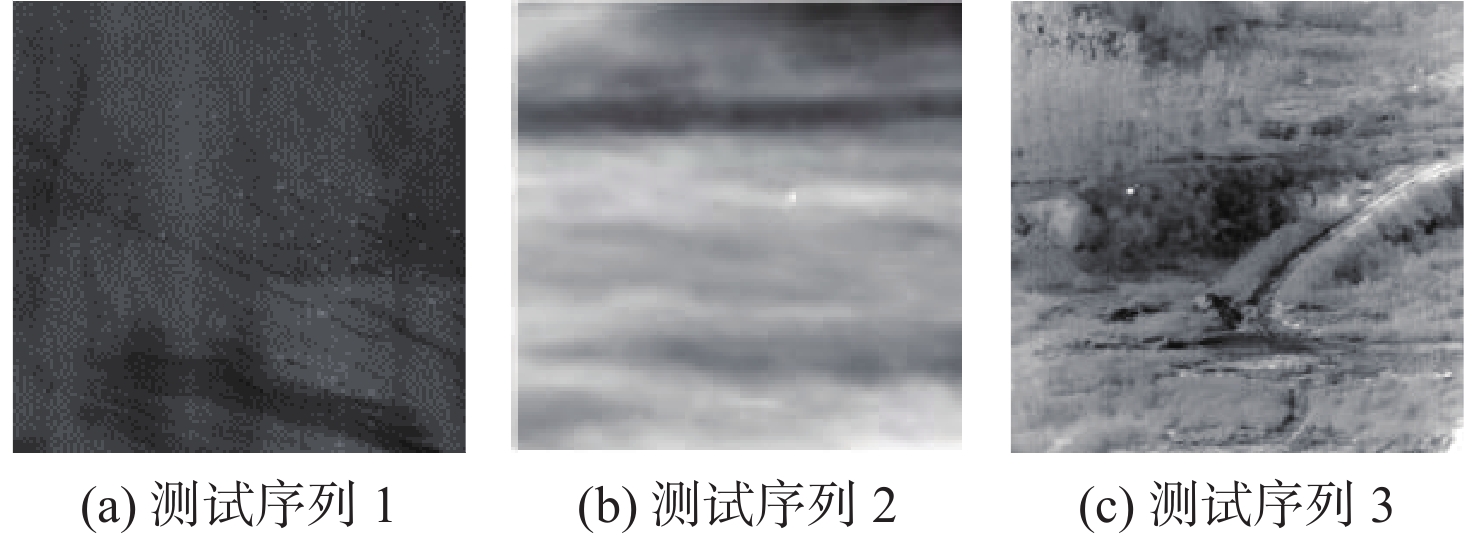

3.1 实验数据集

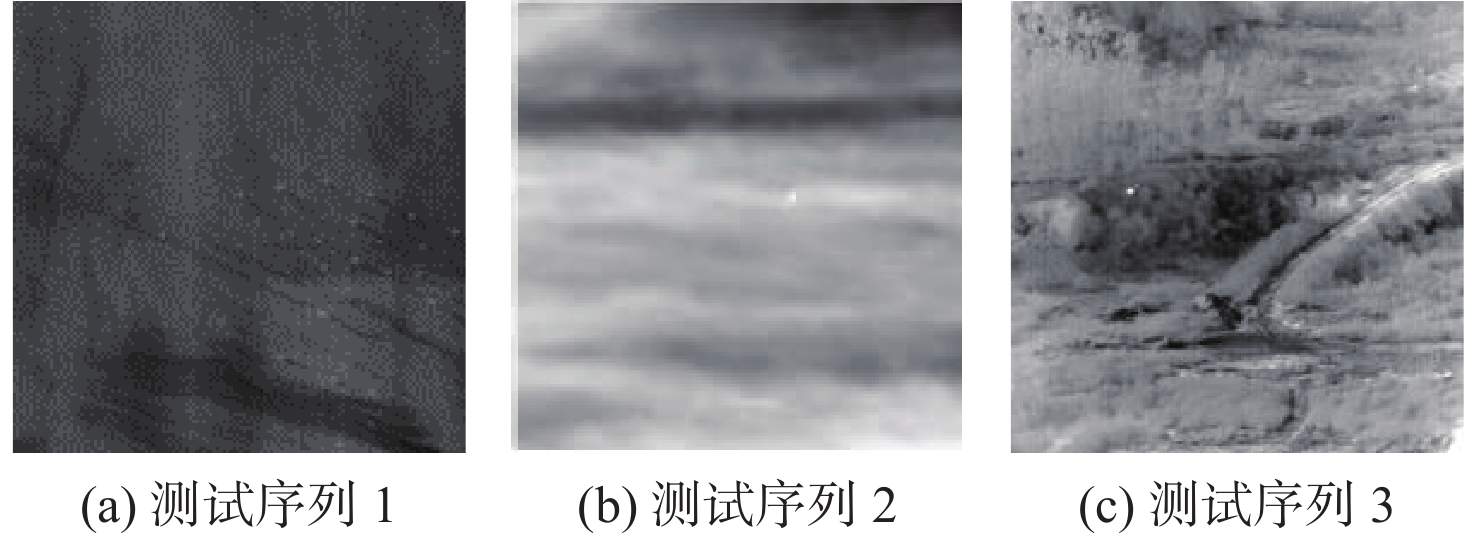

实验数据集针对复杂场景下弱小目标进行设计,包括多种云、地表、空天、海洋等复杂背景类型。数据集建立过程中对图像随机添加不同位置、信噪比和大小的目标到背景图像中,目标位置服从均匀分布,目标信噪比范围为0.5~1,目标尺寸范围为1×1~13×13,并包含条状小目标。训练数据集包含6743幅图像,测试数据集包含3个测试序列共4917幅图像,如表4和图16所示。

3.2 实验与测试平台

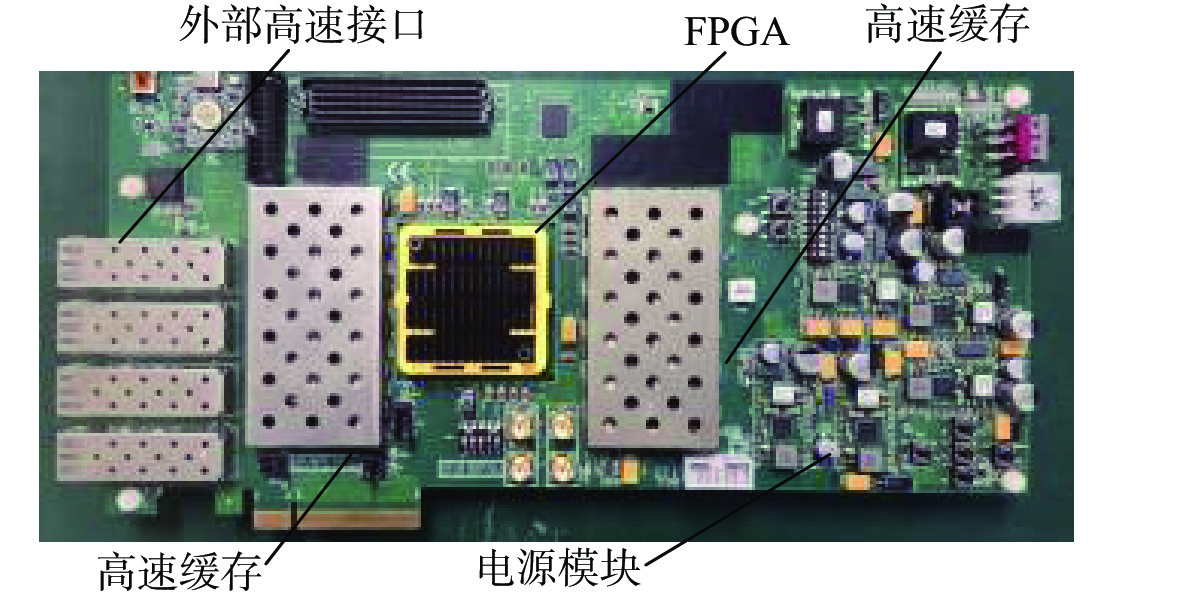

实验与测试平台采用高性能FPGA处理板对EISTDnet的实现予以验证,实物如图17所示。

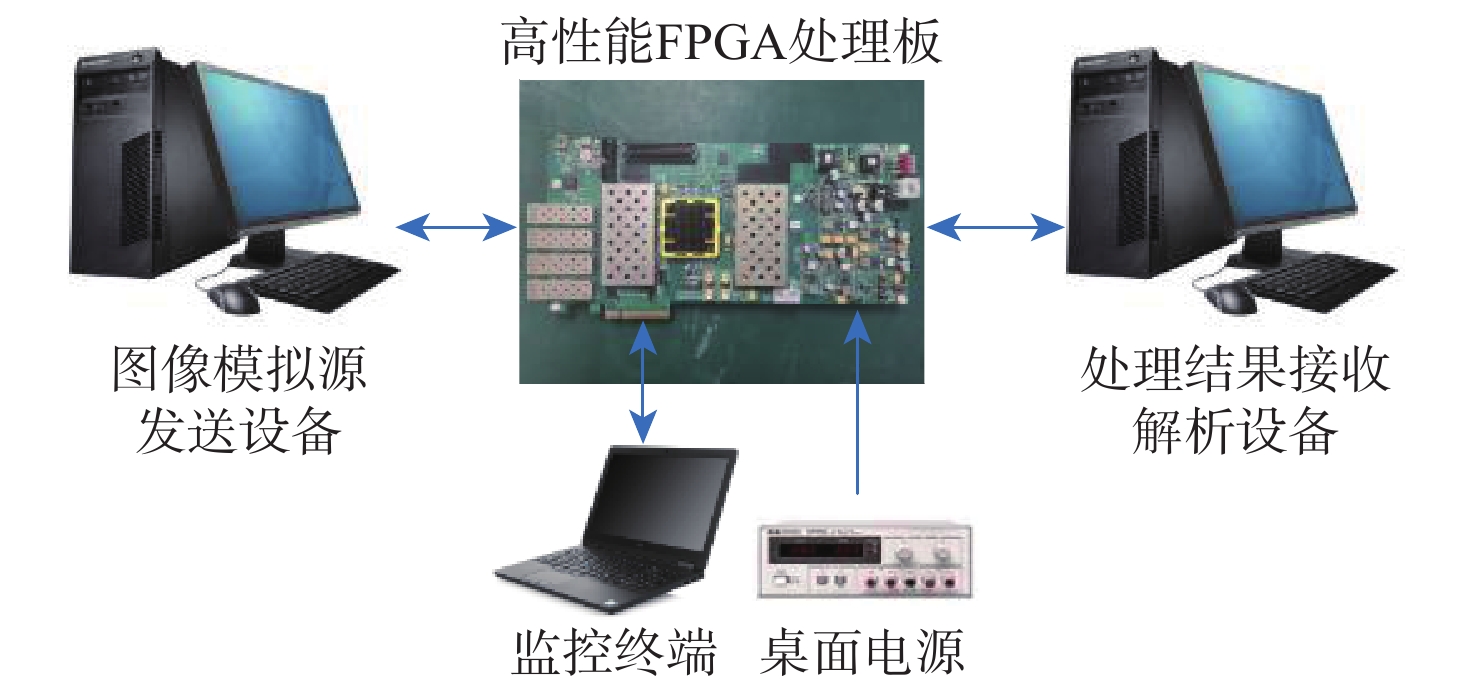

为验证算法处理性能,以高性能FPGA处理板为核心搭建了一套自测试验证系统,系统组成如图18所示。高性能处理板实时接收图像模拟源发送设备输出的测试序列图,由FPGA处理后将结果送至处理结果接收解析设备存储,继而通过解析软件对结果进行分析比对,完成对EISTDnet实现功能性能测试与验证。

3.3 检测性能测试与分析

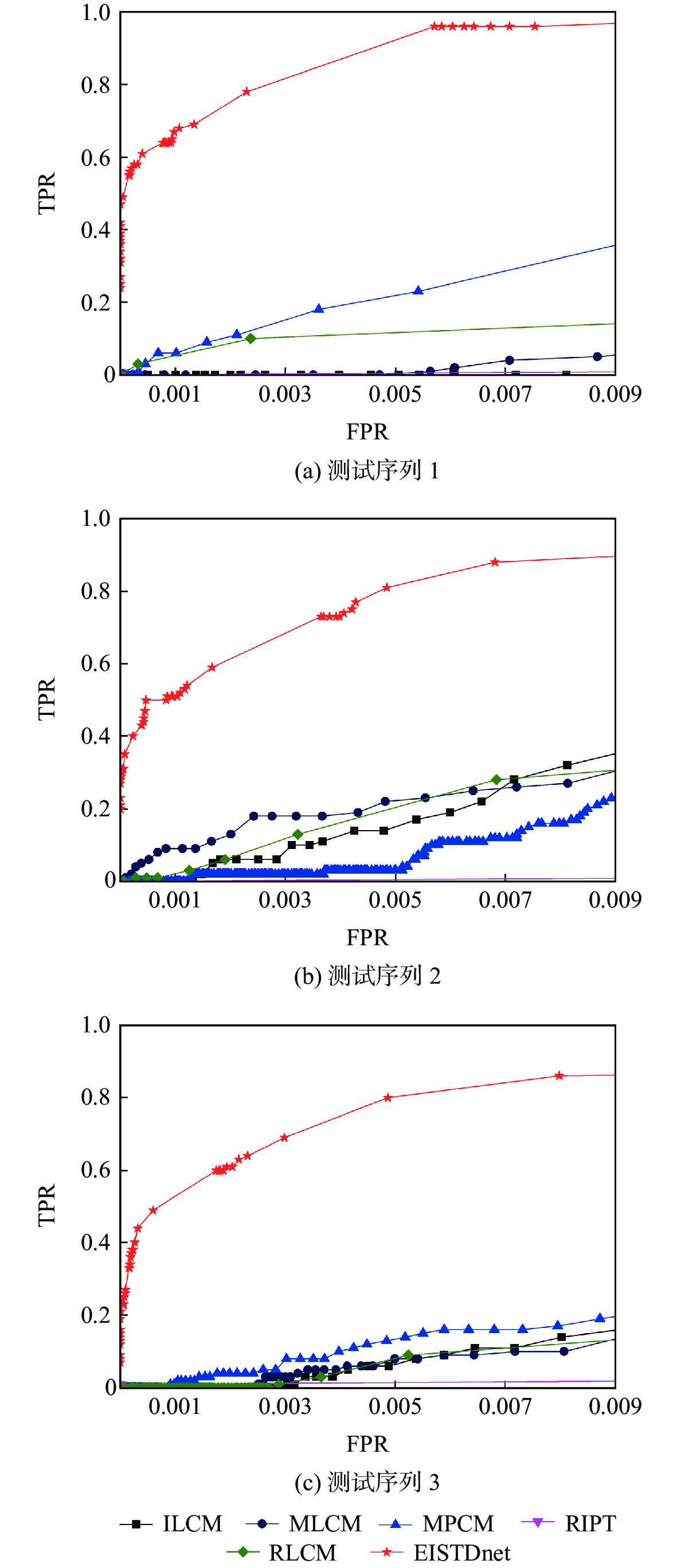

为证明EISTDnet的优越性,本文将其测试结果与ILCM 、MLCM、MPCM、RIPT和RLCM这5种算法的仿真结果进行对比,这些算法的代码来自相应作者的网站。不同算法对应的目标增强结果如图19所示,可以看出EISTDnet相对其他算法具有较明显优势。

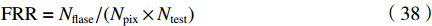

此外,为更系统地描述EISTDnet与其他算法性能比较,采用受试者工作特征(receiver operating characteristic,ROC)曲线作为性能量化指标,曲线中虚警率(false positive rate,FPR)和检测率(true positive rate,TPR)定义如式(38)和式(39)所示。

FRR=Nflase/(Npix×Ntest) (38) TRR=Ntrue/Nreal (39) 式中:

Nfalse 为检出的错误目标数量;Npix 为每张图片像素总数;Ntest 为测试用图片总数;Ntrue 为检出的正确目标数量;Nreal 为测试序列中实际目标数量。图20给出了EISTDnet与其他5种算法在不同测试序列下ROC曲线对比,可以直观看出,本文算法相较其他算法检测率提升明显,在低虚警率(10−3)下3个测试序列平均检测率提升49.5%,充分说明EISTDnet对复杂背景下低信噪比小目标的检测优势。

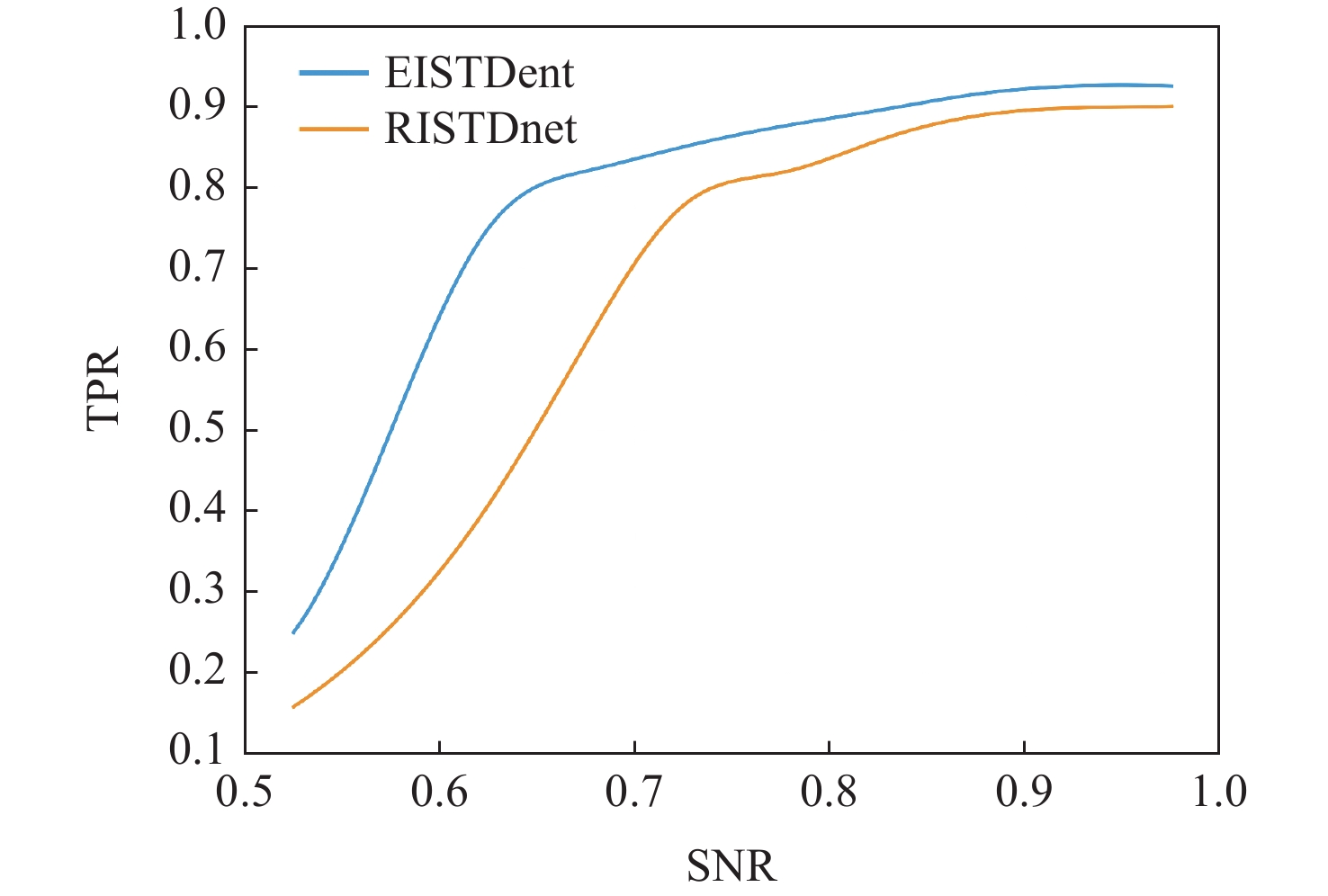

表5给出了EISTDnet与RISTDnet在3个测试序列下的检测率对比。图21给出了不同信噪比下EISTDnet与RISTDnet对条状小目标检测率的对比曲线。从表5和图21可知,EISTDnet与RISTDnet相比检测性能有一定优势,性能差异主要体现在测试序列中信噪比偏低的条状小目标。表6分别统计了各测试序列中信噪比最低的50个条状目标在10−3虚警率下2种网络的检测性能,这些目标信噪比范围为0.5~0.68。

表 5 EISTDnet与RISTDnet目标检测性能对比Table 5. Comparison of target detection performance between EISTDnet and RISTDnet% 项目 EISTDnet RISTDnet 测试序列1 66.97 63.81 测试序列2 50.99 48.65 测试序列3 52.76 50.25 表 6 EISTDnet与RISTDnet条状弱小目标检测性能对比Table 6. Comparison of stripe dim target detection performance between EISTDnet and RISTDnet项目 EISTDnet

目标数/检出数RISTDnet

目标数/检出数测试序列1 50/31 50/15 测试序列2 50/24 50/12 测试序列3 50/27 50/14 平均检测率/% 56.7 27.3 3.4 FPGA实现资源与处理性能分析

表7给出了优化后的检测算法FPGA硬件资源使用情况,FPGA型号为Xilinx公司生产XC7VX690T,开发工具为Vivado 2019.1。

表 7 FPGA资源利用率Table 7. FPGA resource utilization资源 BRAM DSP硬核 触发器 查找表 使用资源 2746 3258 755915 360141 可利用资源 2940 3600 866400 433200 利用率/% 93 91 87 83 从表7中可以看出,为尽可能优化时序并降低外部存储器访问频次,片内BRAM和用来生成REG的触发器(flip flop,FF)利用率分别高达93%与87%。大量BRAM和FF的使用有效保证了并行处理架构无阻塞流水运行,同时,降低了FPGA内布局布线难度,继而提高了系统布局布线后时钟频率。乘除等复杂高精度运算全部使用片内DSP硬核资源,由于卷积并行计算矩阵规模较大,利用率也高达91%。

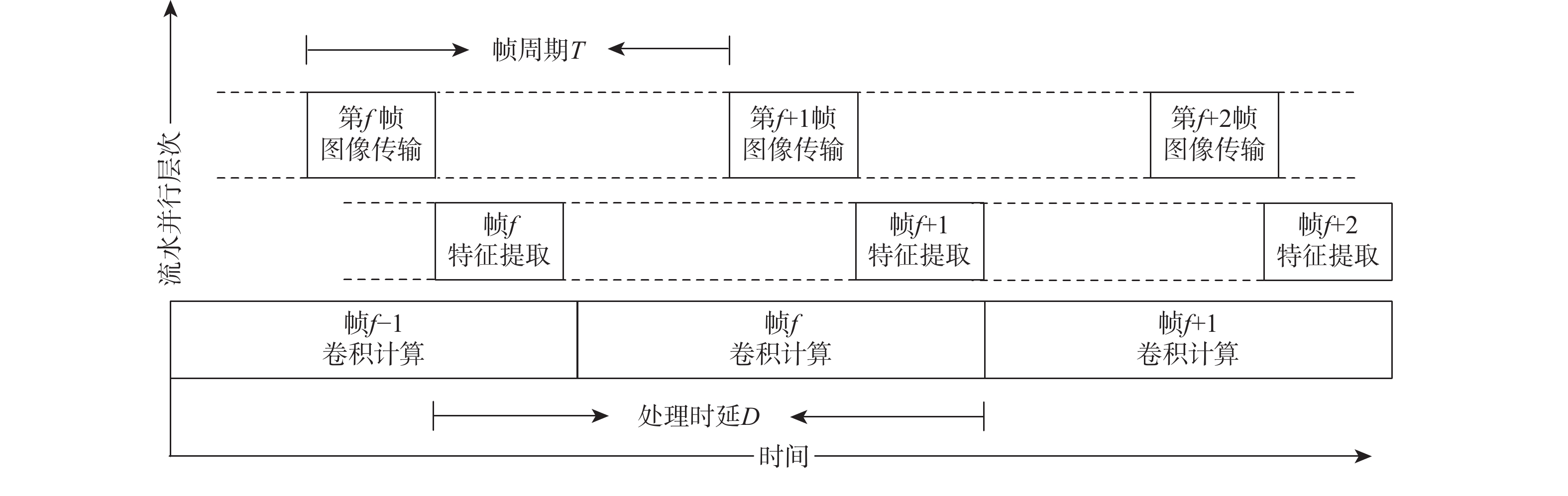

图22给出了EISTDnet网络在FPGA内处理流水线示意图,依据处理流程流水线上主要包括图像传输、特征提取、卷积网络计算3级。其中由于计算规模较大,卷积网络计算占用了流水线上最长处理时间,因而其处理时延决定了FPGA实时流水处理能力。而对于固定尺寸输入图像,卷积网络处理时延取决于网络各层处理循环数量,其仅与循环分块数量、输入通道数量和输出通道数量相关,而这些参数在网络训练后固化,不受图像特性影响,因此,FPGA整体流水处理架构具有良好的稳定性和实时性保障。

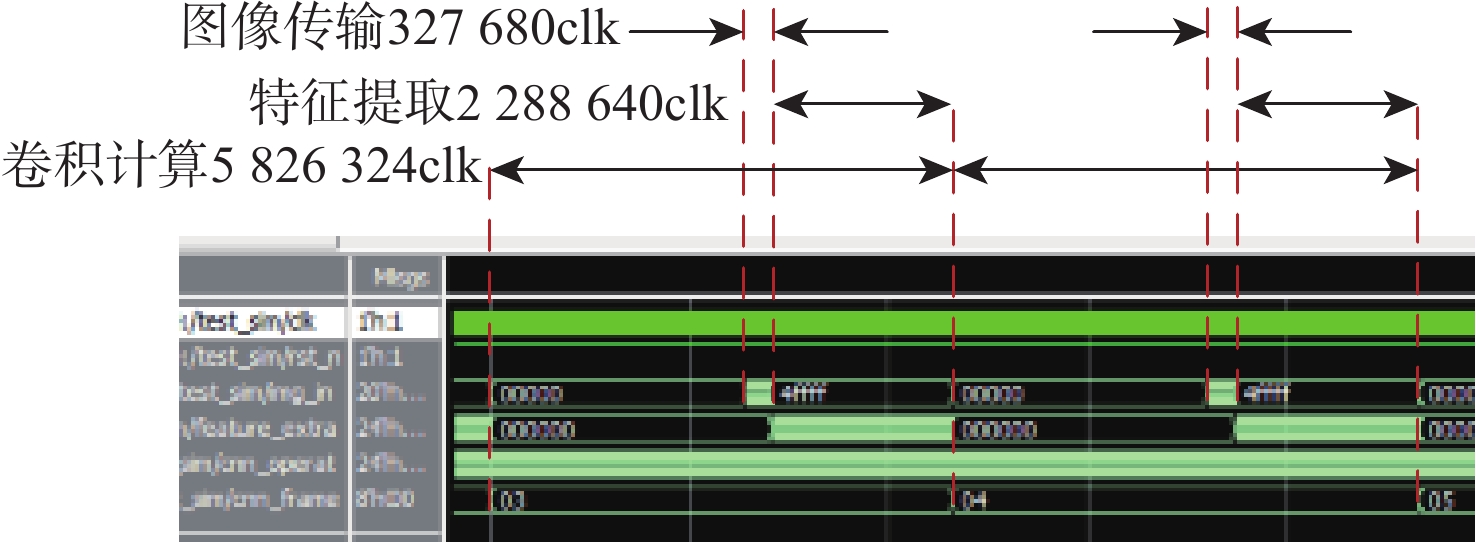

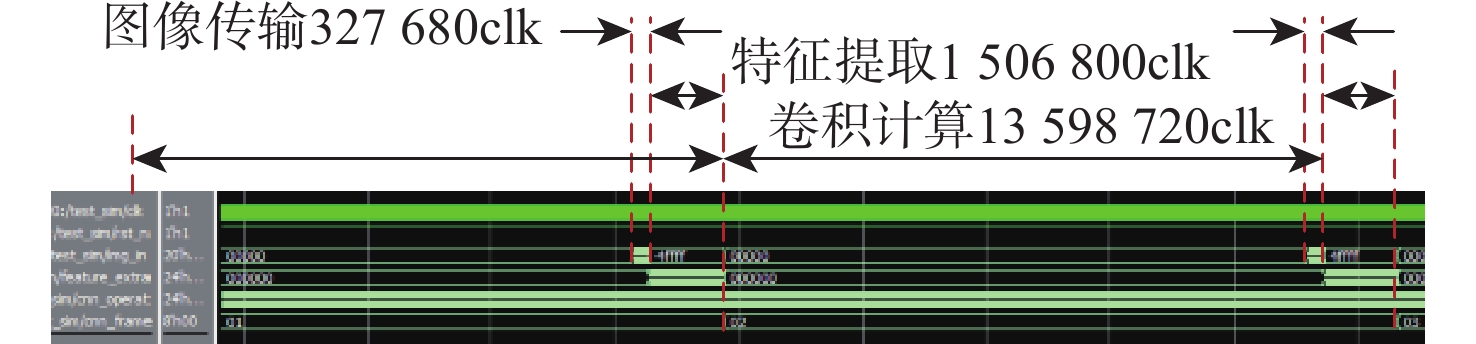

图23给出了EISTDnet的FPGA实现仿真波形。FPGA实现中图像传输、特征提取和卷积计算三部分采用并行流水处理方式,仿真显示单帧图像流水线上最大处理时钟数为5826324个时钟周期(clock period,简称clk)。FPGA布局布线后时钟支持的最高频率为187 MHz,实际片内工作时钟为180 MHz,此时处理周期为32.37 ms,可满足30 Hz、640×512图像快速实时处理需求。

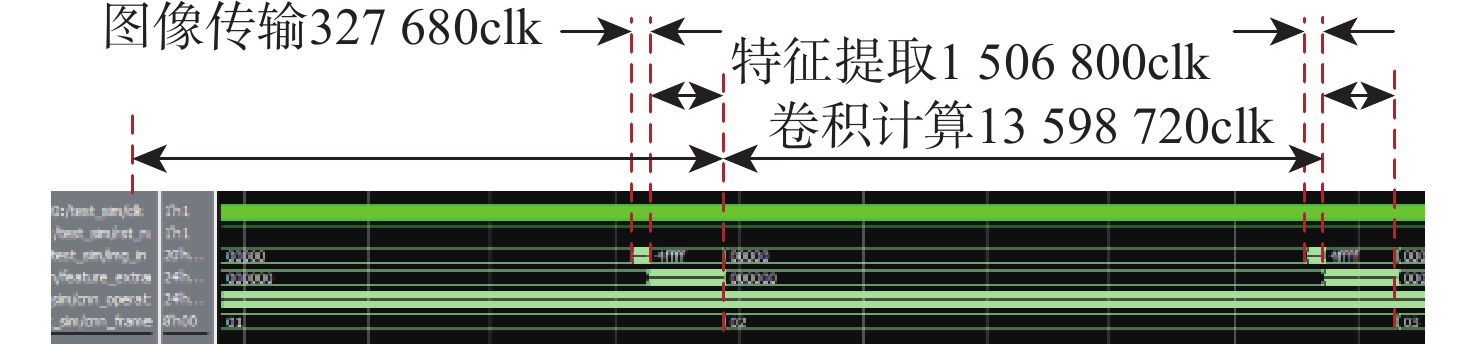

图24给出了同等规模处理架构下RISTDnet的实现仿真波形,仿真显示单帧图像流水线上最大处理时钟数为13598720个时钟周期,180 MHz时钟下处理周期为75.55 ms。对比可见得益于计算操作数的优化和并行处理架构与卷积核尺寸之间的匹配性,EISTDnet在FPGA实时处理速率上相对RISTDnet提高了1.33倍。

4. 结 论

本文面向复杂背景红外弱小目标实时检测难题,提出一种基于深度学习的增强型红外小目标检测网络EISTDnet,并基于FPGA平台实现其高性能实时处理,具体结论如下:

1) EISTDnet可实现较为优异的检测性能,经3个序列共4917幅图像测试,相比传统5种算法,在虚警率为10−3条件下,平均检测率提升49.5%,充分说明EISTDnet对复杂背景下低信噪比红外小目标的检测优势。

2) 针对RISTDnet对复杂背景下条状弱小目标检测性能较弱的问题,EISTDnet通过增加8种定权特征提取卷积核强化特征提取能力,对信噪比范围在0.5~0.68之间的条状小目标,实现了10−3虚警率下29.4%检测率的提升。

3) 由于定权特征图数量增加,EISTDnet运算操作数相对RISTDnet增加了29.23%。通过采用卷积核尺寸归一化、BN层融合和特征映射层简化3种优化算法,EISTDnet运算操作数降低至RISTDnet的48.46%。同时,通过采用数据深度复用算法进一步优化EISTDnet多尺度定权特征提取模块,优化后该模块运算操作数降低至优化前的15.51%。运算操作数的多方面优化显著降低了对处理芯片计算资源的需求。

4) 通过多维循环并行展开、循环计算顺序优化和多级缓存优化算法,构建了EISTDnet高性能并行计算架构,在单片FPGA上实现30 Hz、640×512图像快速实时处理,相比RISTDnet处理速率提高了1.33倍。

为继续提高EISTDnet实时处理性能,拟在后续进一步开展针对该网络的裁剪压缩方法研究,并通过训练与优化网络参数控制裁减压缩后精度损失。

-

表 1 EISTDnet网络参数

Table 1. EISTDnet network parameters

层编号 卷积核

数量卷积核

尺寸/步长输出特征图

尺寸特征提取 512×640 Conv1.1 24 3×3/1 512×640 Conv1.2 24 3×3/1 512×640 Conv1.3 24 3×3/1 512×640 Conv1.4 24 3×3/1 512×640 Conv1.5 32 3×3/1 512×640 Pool1 2×2/2 256×320 Conv2.1 32 3×3/1 256×320 Conv2.2 32 3×3/1 256×320 Conv2.3 64 3×3/1 256×320 Pool2 2×2/2 128×160 Conv3.1 64 3×3/1 128×160 Conv3.2 128 3×3/1 128×160 Pool3 2×2/2 64×80 Conv4 256 3×3/1 64×80 Conv5 64 3×3/1 64×80 表 2 EISTDnet与RISTDnet运算操作数比对

Table 2. Comparison of operands between EISTDnet and RISTDnet

网络改进阶段 运算操作数 RISTDnet 69999411200 EISTDnet强化多尺度特征 90460323840 EISTDnet卷积网络轻量化 33919795200 表 3 图像读取与运算操作比对

Table 3. Image reading and operation comparison

算法 像素读取次数 运算操作数 优化前 607846400 629473280 优化后 39649280 97648640 降低比例/% 6.52 15.51 表 4 测试序列典型帧与数量

Table 4. Typical frames and number of test sequences

表 5 EISTDnet与RISTDnet目标检测性能对比

Table 5. Comparison of target detection performance between EISTDnet and RISTDnet

% 项目 EISTDnet RISTDnet 测试序列1 66.97 63.81 测试序列2 50.99 48.65 测试序列3 52.76 50.25 表 6 EISTDnet与RISTDnet条状弱小目标检测性能对比

Table 6. Comparison of stripe dim target detection performance between EISTDnet and RISTDnet

项目 EISTDnet

目标数/检出数RISTDnet

目标数/检出数测试序列1 50/31 50/15 测试序列2 50/24 50/12 测试序列3 50/27 50/14 平均检测率/% 56.7 27.3 表 7 FPGA资源利用率

Table 7. FPGA resource utilization

资源 BRAM DSP硬核 触发器 查找表 使用资源 2746 3258 755915 360141 可利用资源 2940 3600 866400 433200 利用率/% 93 91 87 83 -

[1] CHEN C L P, LI H, WEI Y, et al. A local contrast method for small infrared target detection[J]. IEEE Transactions on Geoscience and Remote Sensing, 2014, 52(1): 574-581. doi: 10.1109/TGRS.2013.2242477 [2] HAN J, MA Y, ZHOU B, et al. A robust infrared small target detection algorithm based on human visual system[J]. IEEE Geoscience and Remote Sensing Letters, 2014, 11(12): 2168-2172. doi: 10.1109/LGRS.2014.2323236 [3] WEI Y, YOU X, LI H. Multiscale patch-based contrast measure for small infrared target detection[J]. Pattern Recognition, 2016, 58: 216-226. doi: 10.1016/j.patcog.2016.04.002 [4] HAN J, LIANG K, ZHOU B, et al. Infrared small target detection utilizing the multiscale relative local contrast measure[J]. IEEE Geoscience and Remote Sensing Letters, 2018, 15(4): 612-616. doi: 10.1109/LGRS.2018.2790909 [5] YAO S, CHANG Y, QIN X. A coarse-to-fine method for infrared small target detection[J]. IEEE Geoscience and Remote Sensing Letters, 2019, 16(2): 256-260. doi: 10.1109/LGRS.2018.2872166 [6] HAN J, LIU S, QIN G, et al. A local contrast method combined with adaptive background estimation for infrared small target detection[J]. IEEE Geoscience and Remote Sensing Letters, 2019, 16(9): 1442-1446. doi: 10.1109/LGRS.2019.2898893 [7] GAO C, MENG D, YANG Y, et al. Infrared patch-image model for small target detection in a single image[J]. IEEE Transactions on Image Processing, 2013, 22(12): 4996-5009. doi: 10.1109/TIP.2013.2281420 [8] DAI Y, WU Y, SONG Y, et al. Non-negative infrared patch-image model: Robust target-background separation via partial sum minimization of singular values[J]. Infrared Physics and Technology, 2017, 81: 182-194. doi: 10.1016/j.infrared.2017.01.009 [9] DAI Y, WU Y. Reweighted infrared patch-tensor model with both nonlocal and local priors for single-frame small target detection[J]. IEEE Journal of Selected Topics in Applied Earth Observations and Remote Sensing, 2017, 10(8): 3752-3767. doi: 10.1109/JSTARS.2017.2700023 [10] ZHANG L, PENG L, ZHANG T, et al. Infrared small target detection via non-convex rank approximation minimization joint l2, 1 norm[J]. Remote Sensing, 2018, 10(11): 1821. doi: 10.3390/rs10111821 [11] ZHOU F, WU Y, DAI Y, et al. Detection of small target using schatten 1/2 quasi-norm regularization with reweighted sparse enhancement in complex infrared scenes[J]. Remote Sensing, 2019, 11(17): 2058. doi: 10.3390/rs11172058 [12] REN S, HE K, GIRSHICK R, et al. Faster r-cnn: Towards real-time object detection with region proposal networks[J]. IEEE Transactions on Pattern Analysis and Machine Intelligence, 2017, 39(6): 1137-1149. doi: 10.1109/TPAMI.2016.2577031 [13] REDMON J, FARHADI A. Yolo9000: Better, faster, stronger[C]//In 30th IEEE Conference on Computer Vision and Pattern Recognition. Piscataway: IEEE Press, 2014: 6517–6525. [14] JOSEPH R, ALI F. Yolov3: An incremental improvement[EB/OL]. (2018-04-08)[2021-04-21]. http: //arxiv. org/abs/1804.02767. [15] LIU W, ANGUELOV D, ERHAN D, et al. SSD: Single shot multibox detector[C]//in 32th IEEE Conference on Computer Vision and Pattern Recognition. Amsterdam: University of Amsterdam, 2016. [16] HOU Q, WANG Z, TAN F, et al. RISTDnet: Robust infrared small target detection network[EB/OL]. (2020-12-27) [2021-04-20]. https://doi.org/10.1109/LGRS.2021.3050828. [17] 李岩. 基于"高分五号"卫星红外影像的舰船尾迹特征分析[J]. 航天返回与遥感, 2020, 41(5): 106-113.LI Y.The ship wake characterization study based on GF-5 infrared images[J]. Spacecraft Recovery & Remote Sensing,2020,41(5):106-113(in Chinese). 期刊类型引用(3)

1. 孟维超,卞春江,聂宏宾. 复杂背景下低信噪比红外弱小目标检测方法. 计算机工程与应用. 2025(08): 183-193 .  百度学术

百度学术2. 穆向阳,雷妍,王闻博. 一种中值滤波快速系统的FPGA实现. 西安石油大学学报(自然科学版). 2023(02): 128-134 .  百度学术

百度学术3. 蒋康宁,周海,卞春江,汪伶. 基于宇航级FPGA的YOLOv5s网络模型硬件加速. 空间科学学报. 2023(05): 950-962 .  百度学术

百度学术其他类型引用(8)

-

下载:

下载:

下载:

下载:

百度学术

百度学术