-

摘要:

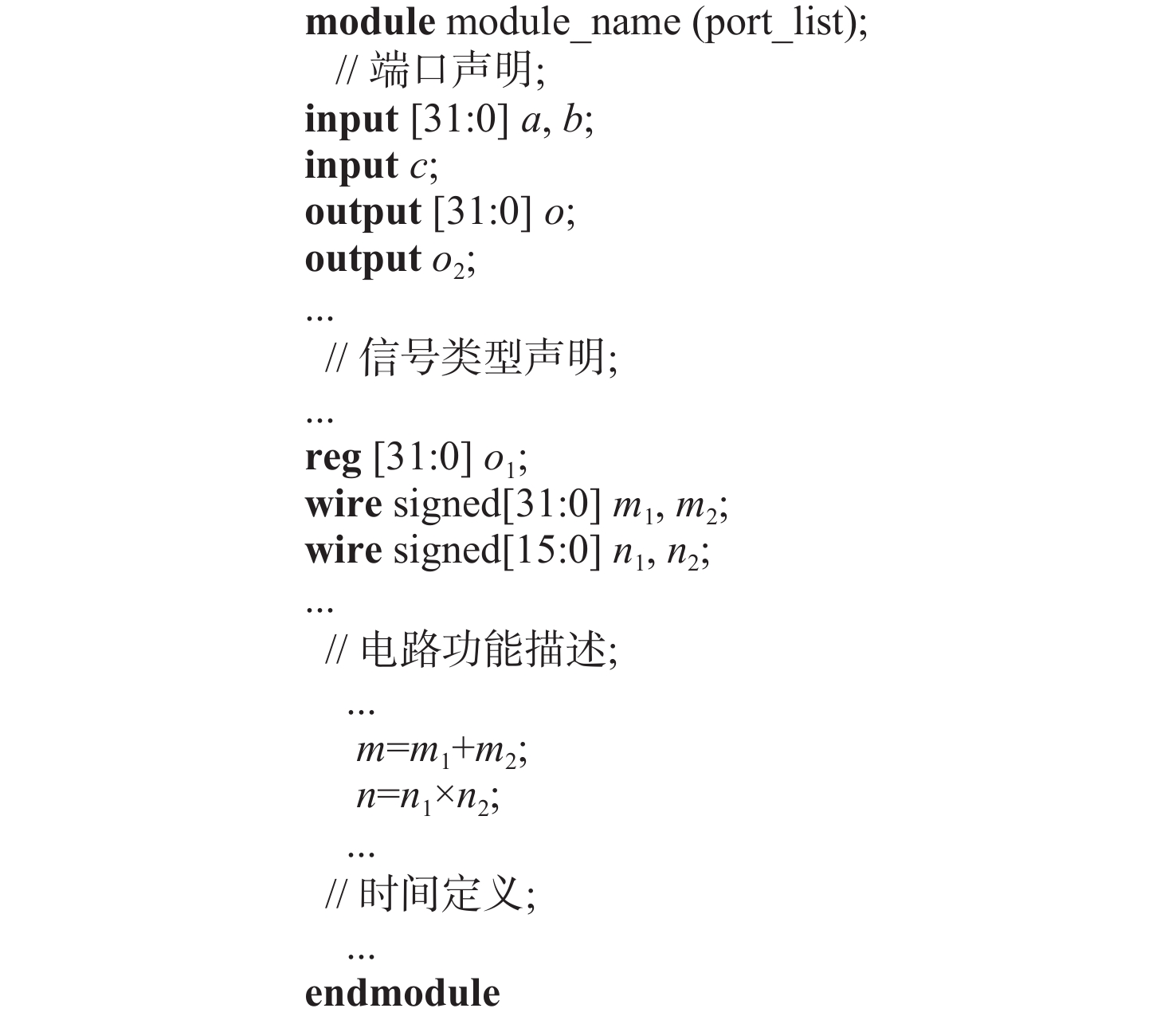

针对基于近似计算技术优化算法在硬件描述语言(HDL)级电路面积优化中不能有效利用结果质量(QoR)约束所提供的优化空间问题,提出了一种包括内部信号位宽优化操作、算术运算符替换操作、近似算术电路调用及近似操作选择机制等算术电路近似优化方法,在QoR约束下实现了电路的面积优化。所提方法使用C语言编程,电路面积用EDA工具Design Compiler结合工艺库进行估算。实验结果显示:与精确优化结果相比,电路面积平均优化55.2%;与现有近似优化方法相比,平均面积优化可进一步获得24.9%提升。

-

关键词:

- 近似计算 /

- 面积优化 /

- HDL级优化 /

- Verilog硬件描述语言 /

- 逻辑综合

Abstract:Given that the current area optimization at the hardware description language (HDL) level using approximate computing techniques is unable to effectively utilize the optimization space provided by quality-of-result (QoR) constraints, an approximate optimization algorithm for arithmetic circuits is proposed. This algorithm includes the selection mechanism of the proposed approximate operations, internal signal bit-width reduction, arithmetic operator replacement, and approximate arithmetic cell circuits calling. The proposed algorithm is programmed in C and the circuit area is estimated by Design Compiler. The experimental results show that under the constraint of QoR, compared with the non-approximate optimization result, the average area saving is 55.2%. The suggested approach can further increase the average area save by 24.9% when compared to the reported approximate strategy.

-

Key words:

- approximate computing /

- area optimization /

- HDL-level optimization /

- Verilog HDL /

- logic synthesis

-

表 1 近似电路库中部分乘法器

Table 1. Multipliers in library of approximate circuits

电路名称 mAE/% wCE/% mRED/% 功耗 面积 mul8s_1KV8 0 0 0 0.425 729.8 mul8s_1L1G 0.52 2.66 27.44 0.126 284.9 mul8s_1KR3 3.08 12.30 135.77 0.052 172.2 表 2 测试激励的数量对QoR的影响

Table 2. Impact of the number of testing vectors on QoRs

电路名称 QoR/% 输入组合

数为100输入组合

数为500输入组合

数为1000 输入组合

数为5000 波动

范围SVM 74.69 75.35 74.56 74.55 0.80 FIR 94.77 94.35 94.34 94.31 0.42 FFT 91.55 92.25 91.92 91.88 0.70 Multi_4 84.77 84.74 85.19 84.61 0.45 Multi_8_3 95.11 94.98 95.14 95.10 0.16 Multi_16 83.01 81.98 81.95 81.77 1.03 Add_8 94.39 94.34 92.71 93.10 0.63 Variance 81.53 81.77 81.65 80.96 0.81 IIR 87.81 87.97 88.10 87.93 0.16 Factorial 80.79 0 表 3 本文方法与其他方法的比较结果

Table 3. Comparison results of the proposed method and other methods

电路名称 电路的输入/输出数量 精确优化

面积设定的

QoR值/%本文面

积优化率/%文献[16]

面积优化率/%本文功耗

优化率/%文献[16]功耗

优化率/%本文延迟

优化率/%文献[16]延迟

优化率/%SVM 68/2 43 858 76.3 78.4 72.2 72.0 70.8 0 0 FIR 27/15 47 823 91.5 60.5 37.7 31.9 36.7 0 0 FFT 258/256 21 423 92.0 45.5 20.5 38.0 48.9 0 0 Multi_4 8/8 220 80.0 79.4 33.5* 83.8 34.5* 85.9 20.3* Multi_8_3 11/11 205 80.0 36.5 36.5* 41.7 41.7* 33.3 33.3* Multi_16 32/32 2949 80.0 87.9 34.0* 94.1 40.1* 64.2 19.5* Add_8 16/9 69 80.0 39.9 12.8* 55.4 14.7* 58.0 14.5* Variance 80/16 11369 80.0 34.2 13.2* 51.4 25.9* 4.5 0* IIR 34/32 49696 80.0 56.1 23.1* 63.3 5.4* 14.1 0.1* Factorial 4/32 11260 80.0 33.1 19.1* 32.2 16.0* 28.2 17.0* 注:“*”表示该实验结果利用文献[16]提供的方法获得。 -

[1] LIU W Q, LOMBARDI F, SHULTE M. A retrospective and prospective view of approximate computing[J]. Proceedings of the IEEE, 2020, 108(3): 394-399. [2] SCARABOTTOLO I, ANSALONI G, CONSTANTINIDES G A, et al. Approximate logic synthesis: a survey[J]. Proceedings of the IEEE, 2020, 108(12): 2195-2213. [3] MITTAL S. A survey of techniques for approximate computing[J]. ACM Computing Surveys, 2016, 48(4): 1-33. [4] SCHLACHTER J, CAMUS V, PALEM K V, et al. Design and applications of approximate circuits by gate-level pruning[J]. IEEE Transactions on Very Large Scale Integration Systems, 2017, 25(5): 1694-1702. [5] SCARABOTTOLO I, ANSALONI G, POZZI L. Circuit carving: a methodology for the design of approximate hardware[C]// Proceedings of the Design, Automation & Test in Europe Conference & Exhibition. Piscataway: IEEE Press, 2018: 545-550. [6] CHANDRASEKHARAN A, SOEKEN M, GROßE D, et al. Approximation-aware rewriting of AIGs for error tolerant applications[C]//Proceedings of the 35th International Conference on Computer-Aided Design. New York: ACM, 2016: 1-8. [7] PASANDI G, PETERSON M, HERRERA M, et al. Deep-PowerX: a deep learning-based framework for low-power approximate logic synthesis[C]//Proceedings of the Proceedings of the ACM/IEEE International Symposium on Low Power Electronics and Design. New York: ACM, 2020: 73-78. [8] MA J X, HASHEMI S, REDA S. Approximate logic synthesis using Boolean matrix factorization[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41(1): 15-28. [9] 王伦耀, 夏银水, 储著飞. 基于近似计算技术的FPRM电路面积优化[J]. 电子学报, 2019, 47(9): 1868-1874.WANG L Y, XIA Y S, CHU Z F. Area optimization of FPRM circuits using approximate computing[J]. Acta Electronica Sinica, 2019, 47(9): 1868-1874(in Chinese). [10] NEPAL K, LI Y T, BAHAR R I, et al. ABACUS: a technique for automated behavioral synthesis of approximate computing circuits[C]//Proceedings of the Design, Automation & Test in Europe Conference & Exhibition. Piscataway: IEEE Press, 2014: 1-6. [11] PRIYADHARSHNI M, KUMARAVEL S. Low power and area efficient error tolerant adder for image processing application[J]. International Journal of Circuit Theory and Applications, 2020, 48(5): 696-708. [12] PRIYADHARSHNI M, KUMARAVEL S. Design of imprecise multipliers by using approximate technique for error resilient applications[J]. Journal of Circuits, Systems and Computers, 2021, 30(7): 2150114. [13] JIANG H L, LIU C, LIU L B, et al. A review, classification, and comparative evaluation of approximate arithmetic circuits[J]. ACM Journal on Emerging Technologies in Computing Systems, 2017, 13(4): 1-34. [14] MRAZEK V, HRBACEK R, VASICEK Z, et al. EvoApprox8b: library of approximate adders and multipliers for circuit design and benchmarking of approximation methods[C]//Proceedings of the Design, Automation & Test in Europe Conference & Exhibition. Piscataway: IEEE Press, 2017: 258-261. [15] SNYDER W. Verilator, the fastest free Verilog HDL simulator[EB/OL]. (2023-05-05)[2023-12-20]. http://www.veripool.org/wiki/verilator. [16] NEPAL K, HASHEMI S, TANN H, et al. Automated high-level generation of low-power approximate computing circuits[J]. IEEE Transactions on Emerging Topics in Computing, 2019, 7(1): 18-30. -

下载:

下载: