-

摘要:

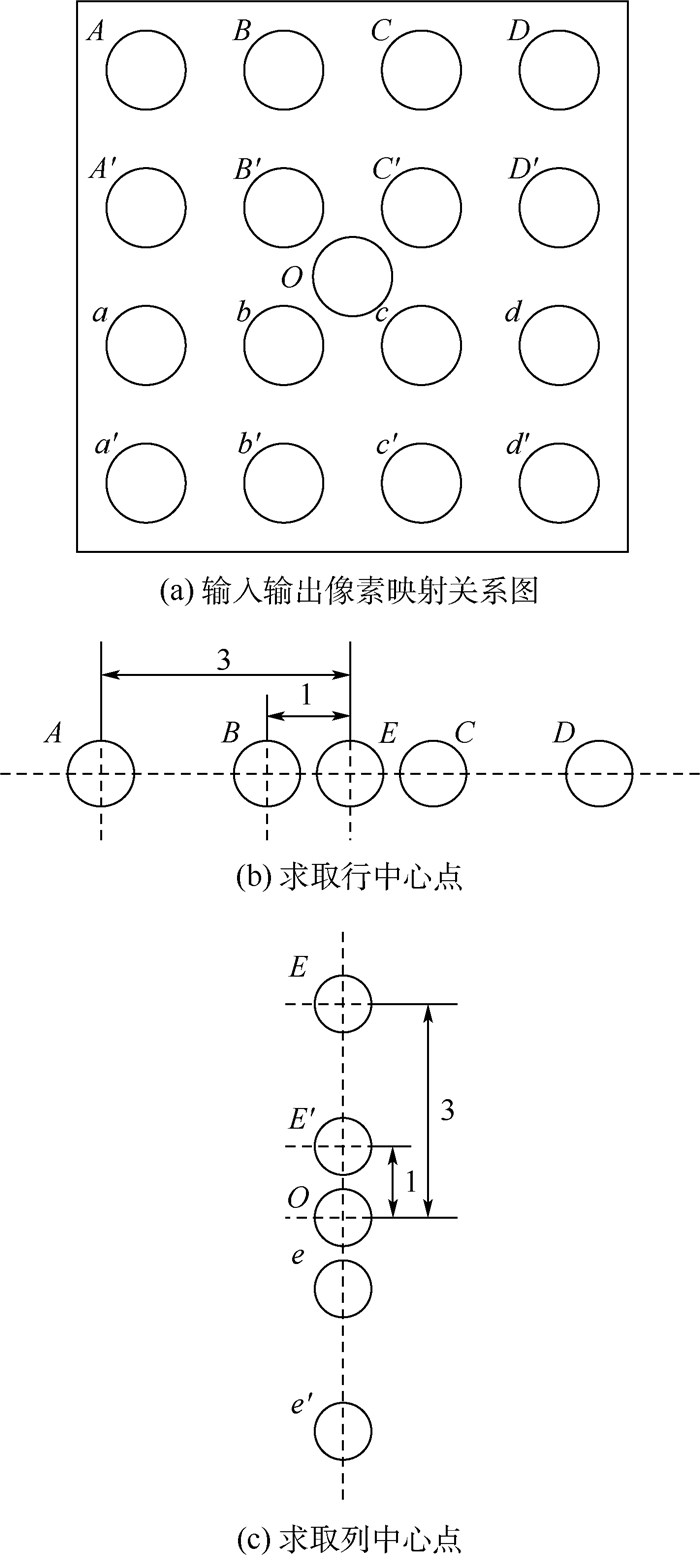

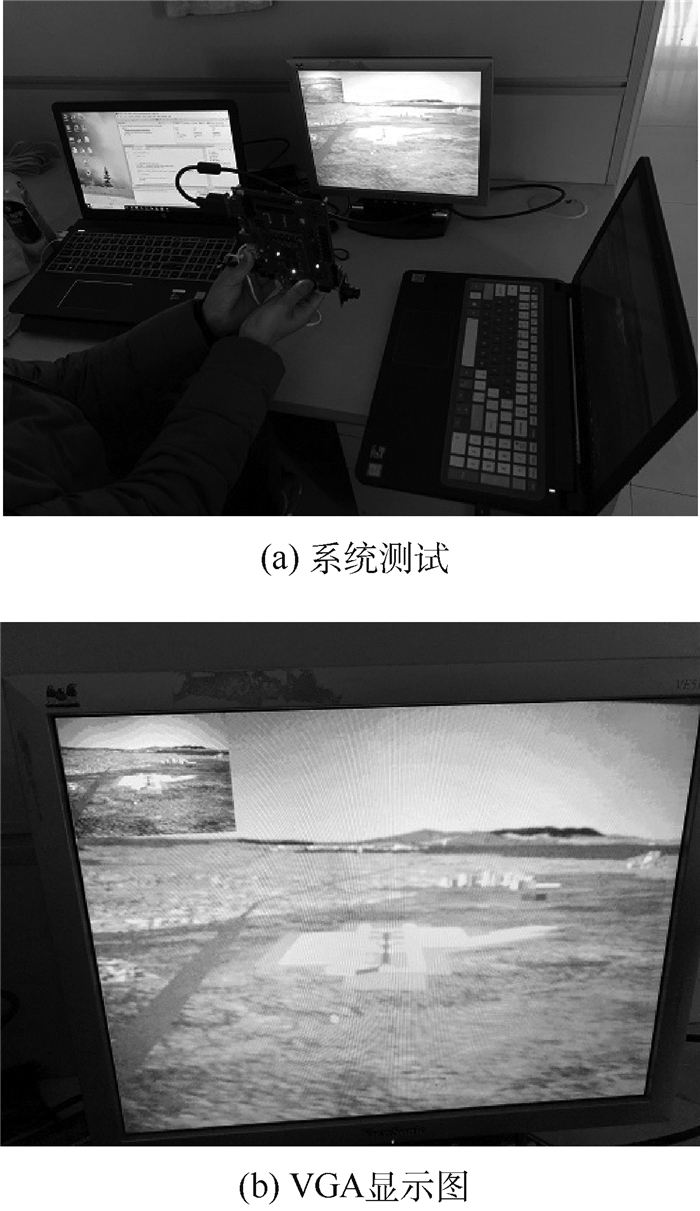

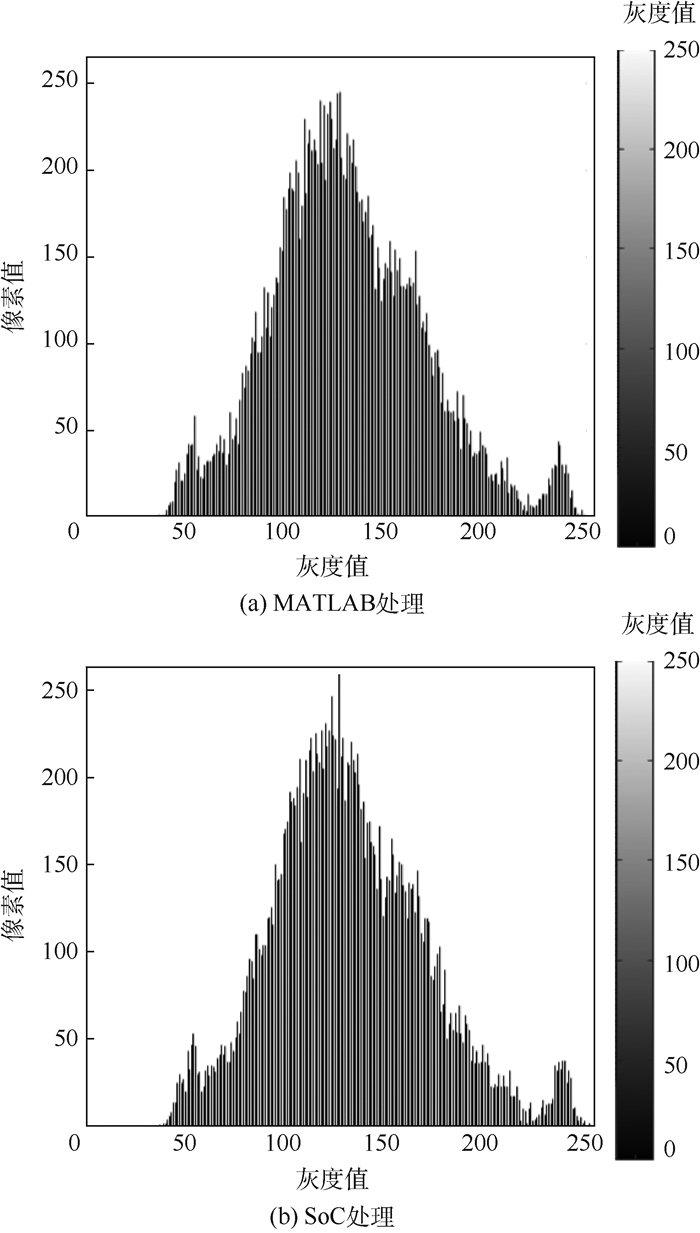

针对无人机自主着陆的跑道检测、识别、跟踪等视觉算法中需要对大量图像进行缩放处理以便后续计算,但又对实时性要求比较高的情况,根据输入输出像素点的映射关系提出了一种适用于硬件加速的图像缩放算法,简化算法结构的同时利用现场可编程门阵列进行模块硬件功能的设计对算法加速,并采用软硬件协同的体系结构搭建实时图像处理系统。实验结果表明,该缩放算法处理精度高、耗时少,且用硬件逻辑实现后,可以进一步提速171倍,硬化后的系统可以通过摄像头获取图像数据,实时处理后在显示器中显示,达到30帧/s的处理速度,可以应用于实时性要求较高的图像处理算法中。

Abstract:Aimed at the problem that a large number of images need to be scaled in the visual algorithm for the runway detection, recognition and tracking of the unmanned aerial vehicle with high real-time requirement, a new image scaling algorithm suitable for hardware acceleration is proposed based on the mapping relation of the input-output pixel. By simplifying the algorithm structure and using the field programmable gate array to design the hardware function of the module, the algorithm accelerates, and the real-time image processing system is built by the software and hardware cooperative architecture. The experimental results show that the improved scaling algorithm has high precision and less time consumption, and it can speed up by 171 times with the hardware logic. The hardened system can get the image data through the camera, and the real-time processing is displayed in the monitor, which has 30 frame/s processing speed. It can be applied to the image processing algorithm with high real-time requirement.

-

表 1 定量分析对比

Table 1. Comparison of quantitative analysis

客观评价指标 最邻近插值 双线性插值 双三次插值 本文算法 left 0.0274 0.0268 0.0257 0.0252 MSE 0.0026 0.0021 0.0020 0.0020 PSNR 25.9162 26.7568 27.0400 27.0521 SNR 18.0160 18.8565 19.1397 19.1518 表 2 4种算法的MATLAB运行时间对比

Table 2. Comparison of MATLAB running time among four algorithms

算法 运行时间/ms 最邻近插值 3.02 双线性插值 13.73 双三次插值 25.66 本文算法 3.44 表 3 本文算法的MATLAB和SoC处理时间对比

Table 3. Comparison of MATLAB and SoC processing time of proposed algorithm

处理方式 处理时间/ms MATLAB 3.44 SoC 0.02 -

[1] RETTKOWSKI J, BOUTROS A, GOHRINGER D.HW/SW co-design of the HOG algorithm on a Xilinx Zynq SoC[J]. Journal of Parallel and Distributed Computing, 2017, 109(1):50-62. [2] KRYJAK T, KOMORKIEWICZ M, GORGON M.Real-time hardware-software embedded vision system for its smart camera implemented in Zynq SoC[J]. Journal of Real-Time Image Processing, 2016, 12(4):1-37. doi: 10.1007/s11554-016-0588-9 [3] SENOUCI B, CHARFI I, HEYRMAN B, et al.Fast prototyping of a SoC-based smart-camera:A real-time fall detection case study[J]. Journal of Real-Time Image Processing, 2016, 12(4):649-662. doi: 10.1007/s11554-014-0456-4 [4] SVETEK A, BLAKE M, HERMIDA M C, et al.The calorimeter trigger processor card:The next generation of high speed algorithmic data processing at CMS[J]. Journal of Instrumentation, 2016, 11(2):201-210. [5] ZARANDY A, NEMETH M, NAGY Z, et al.A real-time multi-camera vision system for UAV collision warning and navigation[J]. Journal of Real-Time Image Processing, 2016, 12(4):709-724. doi: 10.1007/s11554-014-0449-3 [6] 刘镇弢, 李涛, 黄虎才, 等.一种用于实时图像处理的众核结构设计[J].西安电子科技大学学报, 2015, 42(2):95-101. doi: 10.3969/j.issn.1001-2400.2015.02.016LIU Z T, LI T, HUANG H C, et al.A design of the core structure for real-time image processing[J]. Journal of Xidian University, 2015, 42(2):95-101(in Chinese). doi: 10.3969/j.issn.1001-2400.2015.02.016 [7] 杨帆, 张皓, 马新文, 等.基于FPGA的图像处理系统[J].华中科技大学学报(自然科学版), 2015, 43(2):119-123.YANG F, ZHANG H, MA X W, et al.Image processing system based on FPGA[J]. Journal of Huazhong University of Science and Technology(Natural Science Edition), 2015, 43(2):119-123(in Chinese). [8] ZHAI X, ALI A S, AMIRA A, et al.MLP neural network based gas classification system on Zynq SoC[J]. IEEE Access, 2016, 4(2):8138-8146. [9] HAN Y, VIRUPAKSHAPPA K, VITORSILVAPINTO E, et al.Hardware/software co-design of a traffic sign recognition system using Zynq FPGAs[J]. Electronics, 2015, 4(4):1062-1089. doi: 10.3390/electronics4041062 [10] KELLY C, SIDDIQUI F M, BARDAK B, et al.FPGA soft-core processors, compiler and hardware optimizations validated using HOG[C]//International Symposium on Applied Reconfigurable Computing.Berlin: Springer, 2016, 1: 78-90. [11] ALTUNCU M A, GUVEN T, BECERIKLI Y, et al.Real-time system implementation for image processing with hardware/software co-design on the Xilinx Zynq platform[J]. International Journal of Information and Electronics Engineering, 2015, 5(6):473-477. doi: 10.7763/IJIEE.2015.V5.582 [12] KRAJNIK T, SVAB J, PEDRE S, et al.FPGA-based module for SURF extraction[J]. Machine Vision and Applications, 2014, 25(3):787-800. doi: 10.1007/s00138-014-0599-0 [13] GAO F, HUANG Z, WANG S, et al.Optimized parallel implementation of face detection based on embedded heterogeneous many-core architecture[J]. International Journal of Pattern Recognition and Artificial Intelligence, 2017, 31(7):175-180. [14] ISHIKAWA S, TAKAHASHI T, WATANABE S, et al.High-speed X-ray imaging spectroscopy system with Zynq SoC for solar observations[J]. Nuclear Instruments and Methods in Physics Research Section A:Accelerators, Spectrometers, Detectors and Associated Equipment, 2017, 22(1):40-52. [15] CAI W, XU Z, LI Z.A high performance surf image feature detecting system based on Zynq[J]. DEStech Transactions on Computer Science and Engineering, 2017, 11(2):101-110. [16] 王博.数字图像缩放及其质量评价方法研究[D].哈尔滨: 哈尔滨工程大学, 2015: 97-105.WANG B.Digital image zoom and its quality evaluation method[D]. Harbin: Harbin Engineering University, 2015: 97-105(in Chinese). 期刊类型引用(4)

1. 周红华,黄辰,肖伟剑,陈向进,兰景权,许志刚,汪倍吉. 移动通信基站电磁辐射环境影响仿真预测与评价. 环境影响评价. 2020(03): 57-62 .  百度学术

百度学术2. 周红华,黄辰,肖伟剑,陈向进,兰景权,汪倍吉,许志刚. ±45°双极化通讯基站正向地面电磁辐射随角度变化的预测——通讯基站50m内电磁辐射环境超标范围3D准确仿真预测实验之二. 海峡科学. 2019(01): 8-13 .  百度学术

百度学术3. 吴雅琴,杨硕,师兰兰. 基于位置指纹与PDR融合的室内定位算法研究. 矿业科学学报. 2019(05): 448-454 .  百度学术

百度学术4. 周红华,黄辰,肖伟剑,兰景权,陈向进,许志刚,汪倍吉. 通讯基站50m内轴向发射电磁辐射预测——通讯基站50m内电磁辐射环境超标范围3D准确仿真预测实验之一. 海峡科学. 2018(11): 27-31 .  百度学术

百度学术其他类型引用(1)

-

下载:

下载:

百度学术

百度学术