A residue codes and berger codes combined coding self-check method for embryonic electronic cell

-

摘要:

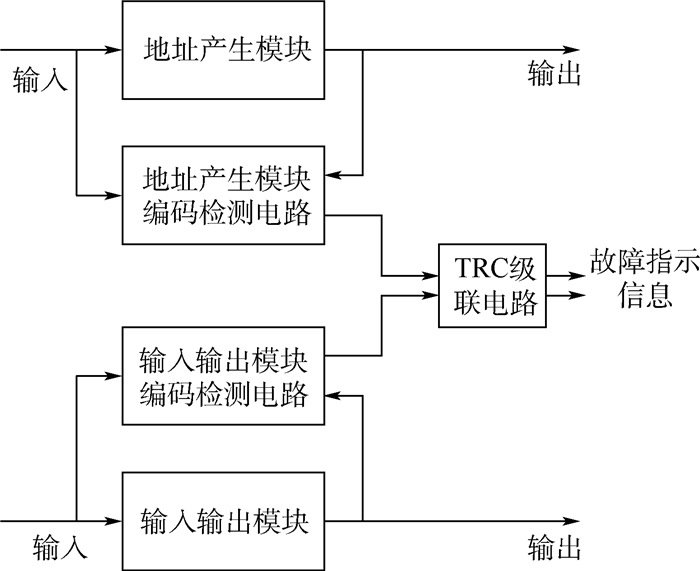

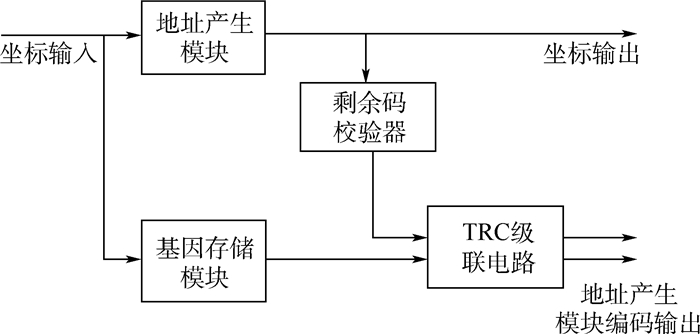

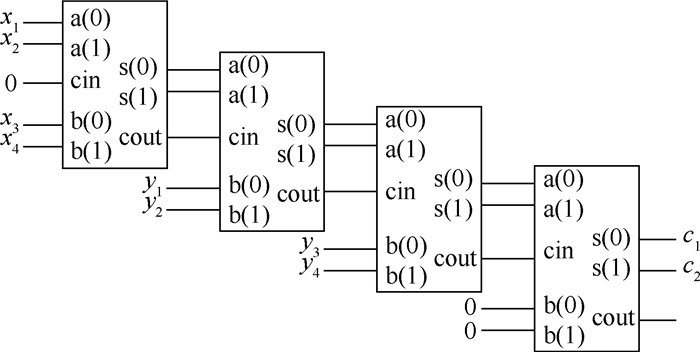

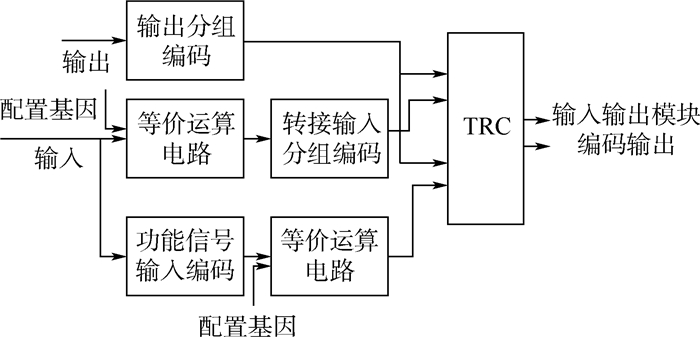

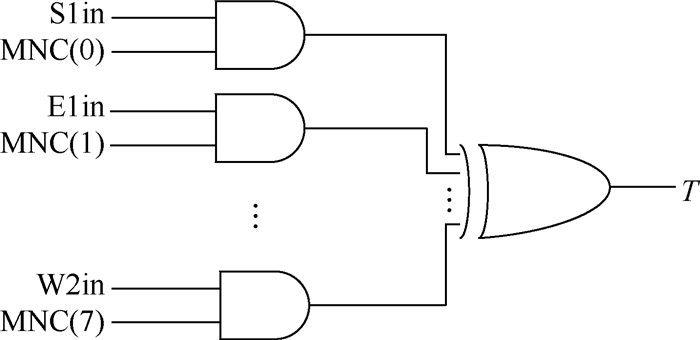

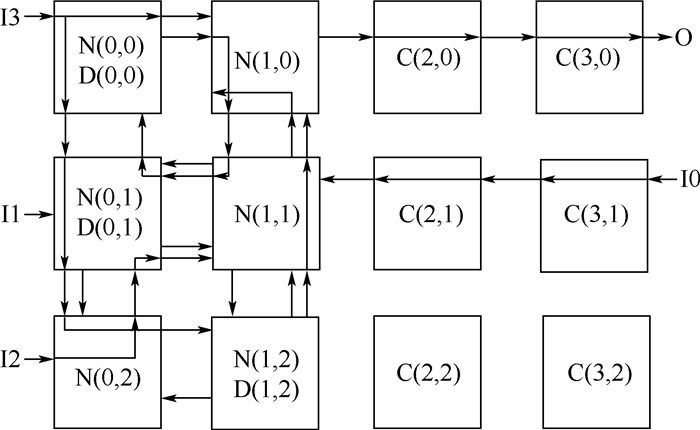

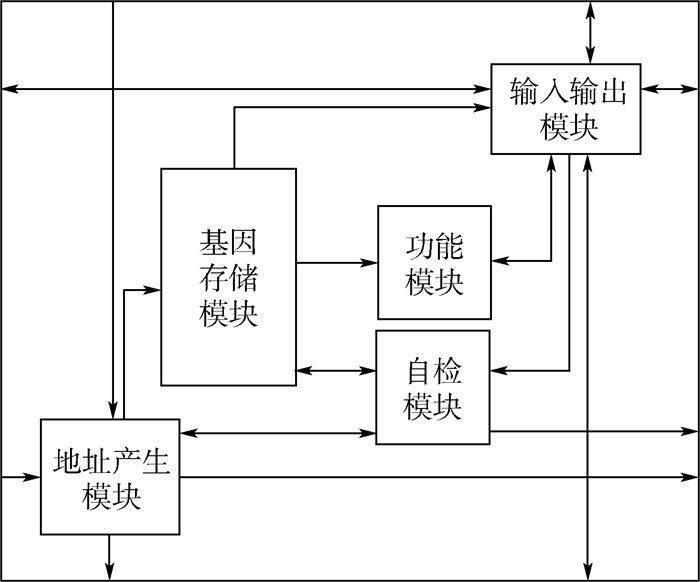

为了更好地实现胚胎电路的自检需求,针对地址产生模块和输入输出模块,基于基本逻辑和算术运算中操作数和结果数之间的剩余码和berger码关系,对胚胎电子细胞输入输出等价运算的构建进行了讨论分析。通过剩余码检测单个故障,berger码检测多位单向故障,设计了一种剩余码/berger码联合编码的胚胎电子细胞自检方法。给出了所提方法的流程和实现方法,分析了基于所提方法设计的胚胎电子细胞的故障检测率、自检模块自检率和硬件资源消耗。以时序逻辑电路为目标电路进行了仿真实验,验证了所提方法对胚胎电子细胞各模块的检测能力和对检测模块的自检能力。

Abstract:According to embryonic electronic cell self-check demand, the residue code and berger code relationships between operands and results are analyzed based on basic logic and arithmetic operations. Aimed at address generator and I/O router, embryonic electronic cell equality operation is analyzed between inputs and outputs. With single fault detected by residue code and multiple bits unidirectional fault detected by berger code, a residue and berger combined coding self-check method is proposed. The process and realization of the proposed method are presented, and the checker is designed. Embryonic electronic cell fault detection rate, self-detection rate and hardware resource consumption based on the proposed method are analyzed. A simulation experiment is presented based on a sequential logic circuit to verify fault detection ability and self-check ability of the proposed method to various modules of embryonic electronic cell.

-

Key words:

- embryonic electronic /

- residue codes /

- self-check /

- online fault detection /

- self-repair

-

表 1 基本逻辑和算术运算中操作数与结果数之间berger码的关系

Table 1. Berger code relationships between operands and results of basic logic and arithmetic operations

运算类别 berger码关系式 与 B(S)=B(X)+B(Y)-B(X|Y) 或 B(S)=B(X)+B(Y)-B(X & Y) 异或 B(S)=B(X)+B(Y)-2B(X & Y) 加 B(S)=B(X)+B(Y)-B(C)-B(cout) 减 B(S)=B(X)-B(Y)-B(C)-B(cout)+n+1 乘 B(S)=B(X)×B(Y)-B(C) 表 2 LUT输入和编码后LUT功能配置基因

Table 2. LUT inputs and coded LUT function configuration genes

LUT输入 LUT功能配置基因为0的编码后基因 LUT功能配置基因为1的编码后基因 0000 00 11 0001 01 10 0010 01 10 0011 00 11 0100 01 10 0101 00 11 0110 00 11 0111 01 10 1000 01 10 1001 00 11 1010 00 11 1011 01 10 1100 00 11 1101 01 10 1110 01 10 1111 00 11 表 3 基本逻辑单元的硬件资源消耗

Table 3. Hardware consumption of basic logic units

基本逻辑单元 MOS管个数 NAND 4 AND 4 NOR 4 OR 6 NXOR 9 XOR 9 DFF 24 表 4 不同输入输出模块宽度和剩余码模的胚胎电子细胞与经典胚胎电子细胞硬件资源消耗比

Table 4. Hardware consumption ratio of embryonic electronic cell with different I/O router widths and residue code modules to classical embryonic electronic cell

输入输出模块宽度 胚胎电子细胞与经典胚胎电子细胞硬件资源消耗比/% 剩余码模为1 剩余码模为3 剩余码模为7 2 193 197 201 3 197 201 204 4 201 204 207 表 5 s27电路各胚胎电子细胞的基因

Table 5. Gene of embryonic electronic cells of s27 circuit

细胞坐标 基因 (0, 0) 1_8515_610F_82_7_020C_3C0_0899 (0, 1) 0_5542_9466_99_4_004E_13B_FDF0 (0, 2) 2_5555_6996_0A_0_0000_649_0000 (1, 0) 1_5555_6996_00_0_0000_000_0000 (1, 1) 0_1608_E1EE_4D_B_082F_616_8878 (1, 2) 2_5150_966B_8B_4_C0B3_EC1_FFFD (2, 0) 1_5555_6996_0A_0_0000_649_0000 (2, 1) 0_5555_6996_00_0_0000_000_0000 (2, 2) 2_6454_F08E_84_4_1430_E89_9918 (3, 0) 1_5450_E996_00_7_30F0_4BF_8000 (3, 1) 2_5555_6996_00_0_0000_000_0000 (3, 2) 3_5555_6996_00_0_0000_000_0000 表 6 s27电路各胚胎电子细胞的故障检测率

Table 6. Fault detection rate for embryonic electronic cells of s27 circuit

坐标 fDR/% fSDR/% LUT DFF 输入输出模块 地址产生模块 基因存储模块 自检模块 (0, 0) 100 100 100 100 100 100 (0, 1) 100 100 100 100 100 100 (0, 2) 100 100 100 100 100 (1, 0) 100 100 100 100 100 (1, 1) 100 100 100 100 100 (1, 2) 100 100 100 100 100 100 (2, 0) 100 100 100 100 100 (2, 1) 100 100 100 100 100 (2, 2) 100 100 100 100 100 (3, 0) 100 100 100 100 100 (3, 1) 100 100 100 100 100 (3, 2) 100 100 100 100 100 表 7 不同检测方法的检测性能

Table 7. Detection performance of different check methods

检测方法 平均故障检测率/% 硬件资源消耗比/% 基因存储模块编码检测 51 113 功能模块双模冗余 65 136 联合编码自检方法 100 197 -

[1] 王涛, 蔡金燕, 孟亚峰, 等. 胚胎电子细胞阵列中空闲细胞的配置[J]. 航空学报, 2017, 38(4): 320266.WANG T, CAI J Y, MENG Y F, et al. Configuration of idle cells in embryonic electronic cell array[J]. Acta Aeronautica et Astronautica Sinica, 2017, 38(4): 320266(in Chinese). [2] ANGE D, SIPPER M, MARCHAL P.Embryonic electronics[J]. BioSystems, 1999, 51(3): 145-152. doi: 10.1016/S0303-2647(99)00052-0 [3] 张砦, 王友仁. 应用设计过程的胚胎硬件细胞单元粒度优化方法[J]. 航空学报, 2016, 37(11): 3502-3511.ZHANG Z, WANG Y R.Cell granularity optimization method of embryonics hardware in application design process[J]. Acta Aeronautica et Astronautica Sinica, 2016, 37(11): 3502-3511(in Chinese). [4] 李岳, 王南天, 钱彦岭. 原核细胞仿生自修复电路设计[J]. 国防科技大学学报, 2012, 34(3): 154-157. doi: 10.3969/j.issn.1001-2486.2012.03.030LI Y, WANG N T, QIAN Y L.Self-healing circuit design inspired by prokaryotic cell[J]. Journal of National University of Defense Technology, 2012, 34(3): 154-157(in Chinese). doi: 10.3969/j.issn.1001-2486.2012.03.030 [5] 徐佳庆, 窦勇, 吕启, 等. 电子组织: 一种具有自适应能力的可重构仿生硬件结构[J]. 计算机研究与发展, 2012, 49(9): 2005-2017.XU J Q, DOU Y, LV Q, et al. eTissue: An adaptive reconfigurable bio-inspired hardware architecture[J]. Journal of Computer Research and Development, 2012, 49(9): 2005-2017(in Chinese). [6] BRADLEY D, ORTEGA-SANCHEZ C, TYRRELL A M.Embryonics+immunotronics: A bio-inspired approach to fault tolerance[C]//Proceedings of 2nd NASA/DoD Workshop on Evolvable Hardware.Piscataway: IEEE Press, 2000: 215-223. [7] 李丹阳, 蔡金燕, 孟亚峰, 等. 基于双模冗余的胚胎电子细胞阵列在线故障检测[J]. 北京航空航天大学学报, 2017, 43(6): 1112-1122. doi: 10.13700/j.bh.1001-5965.2016.0745LI D Y, CAI J Y, MENG Y F, et al. Online fault detection based on dual modular redundancy for embryonics array[J]. Journal of Beijing University of Aeronautics and Astronautics, 2017, 43(6): 1112-1122(in Chinese). doi: 10.13700/j.bh.1001-5965.2016.0745 [8] MANGE D, SANCHEZ E, STAUFFER A, et al. Embryonics: A new methodology for designing field-programmable gate arrays with self-repair and self-replicating[J]. IEEE Transactions on Very Large Scale Integration(VLSI) Systems, 1998, 6(3): 387-399. doi: 10.1109/92.711310 [9] BRADLEY D, TYRRELL A M.The architecture for a hardware immune system[C]//Proceedings of 3rd NASA/DoD Workshop on Evolvable Hardware.Piscataway: IEEE Press, 2001: 193-200. [10] PRODAN L, UDRESCU M, VLADUTIU M, et al.Self-repairing embryonic memory arrays[C]//Proceedings of 6th NASA/DoD Conference on Evolvable Hardware.Piscataway: IEEE Press, 2004: 130-137. [11] YANG S S, WANG Y R.A new self-repairing digital circuit based on embryonic cellular array[C]//Proceedings of 2006 8th International Conference on Solid State and Integrated Circuit Technology.Piscataway: IEEE Press, 2006: 1997-1999. [12] 郝国锋, 王友仁, 张砦, 等. 可重构硬件芯片级故障定位与自主修复方法[J]. 电子学报, 2012, 40(2): 384-388.HAO G F, WANG Y R, ZHANG Z, et al. In-chip fault localization and self-repairing method for reconfigurable hardware[J]. Acta Electronica Sinica, 2012, 40(2): 384-388(in Chinese). [13] FUJIAWARA H.Logic testing and design for testability[M]. Cambridge: MIT Press, 1985: 1-10. [14] WANG L T, WU C W, WEN X Q.VLSI test principles and architectures: Design for testability[M]. Amsterdam: Elsevier, 2006: 37-104. [15] 王继业. 数字电路在线故障检测方法研究[D]. 哈尔滨: 哈尔滨工业大学, 2012: 2-17.WANG J Y.Research on on-line detecting methods of faults reside in digital circuits[D].Harbin: Harbin Institute of Technology, 2012: 2-17(in Chinese). [16] ABRAMOVICI M, BREUER M A, FREDMAN A D. 数字系统测试和可测性设计[M]. 北京: 清华大学出版社, 2004: 4-175.ABRAMOVICI M, BREUER M A, FRIEDMAN A D.Digital systems testing and testable design[M]. Beijing: Tsinghua University Press, 2004: 4-175(in Chinese). [17] 李丹阳, 蔡金燕, 孟亚峰, 等. 基因循环存储模块的SEU自检[J]. 半导体技术, 2016, 41(4): 312-318.LI D Y, CAI J Y, MENG Y F, et al. SEU self-checking of gene cyclic memory module[J]. Semiconductor Technology, 2016, 41(4): 312-318(in Chinese). [18] 邢克飞, 杨俊, 王跃科. FPGA运算单元单粒子错误的Berger/余数联合结果校验法[J]. 宇航学报, 2011, 32(9): 2045-2050. doi: 10.3873/j.issn.1000-1328.2011.09.025XING K F, YANG J, WANG Y K.A Berger and remainder combined result checking approach for errors in FPGA's operation units induced by single event effect[J]. Journal of Astronautics, 2011, 32(9): 2045-2050(in Chinese). doi: 10.3873/j.issn.1000-1328.2011.09.025 [19] HILDER J A, WALKER J A, TYRRELL A M.Optimising variability tolerant standard cell libraries[C]//Proceedings of 2009 IEEE Congress on Evolutionary Computation.Piscataway: IEEE Press, 2009: 2273-2280. -

下载:

下载: