-

摘要:

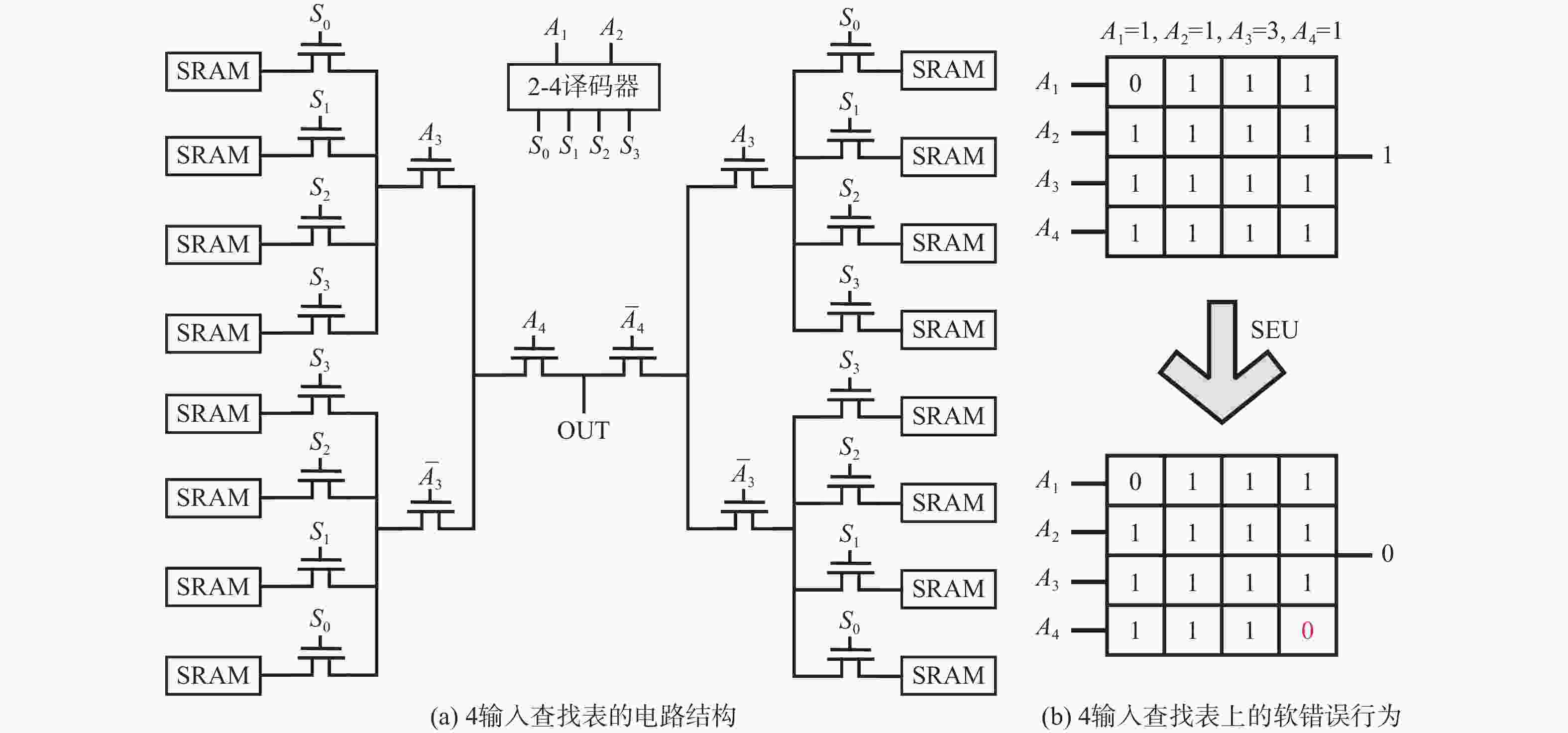

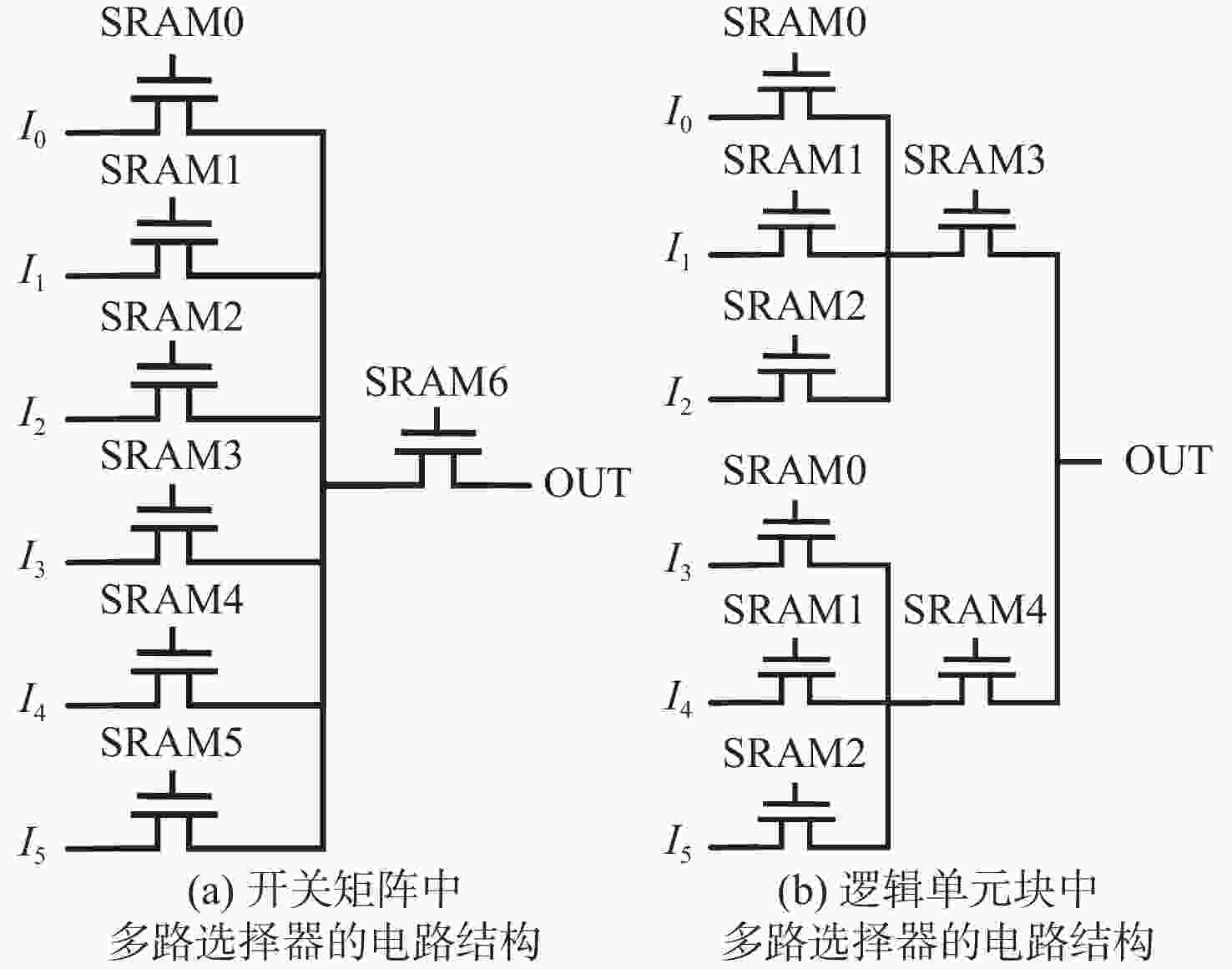

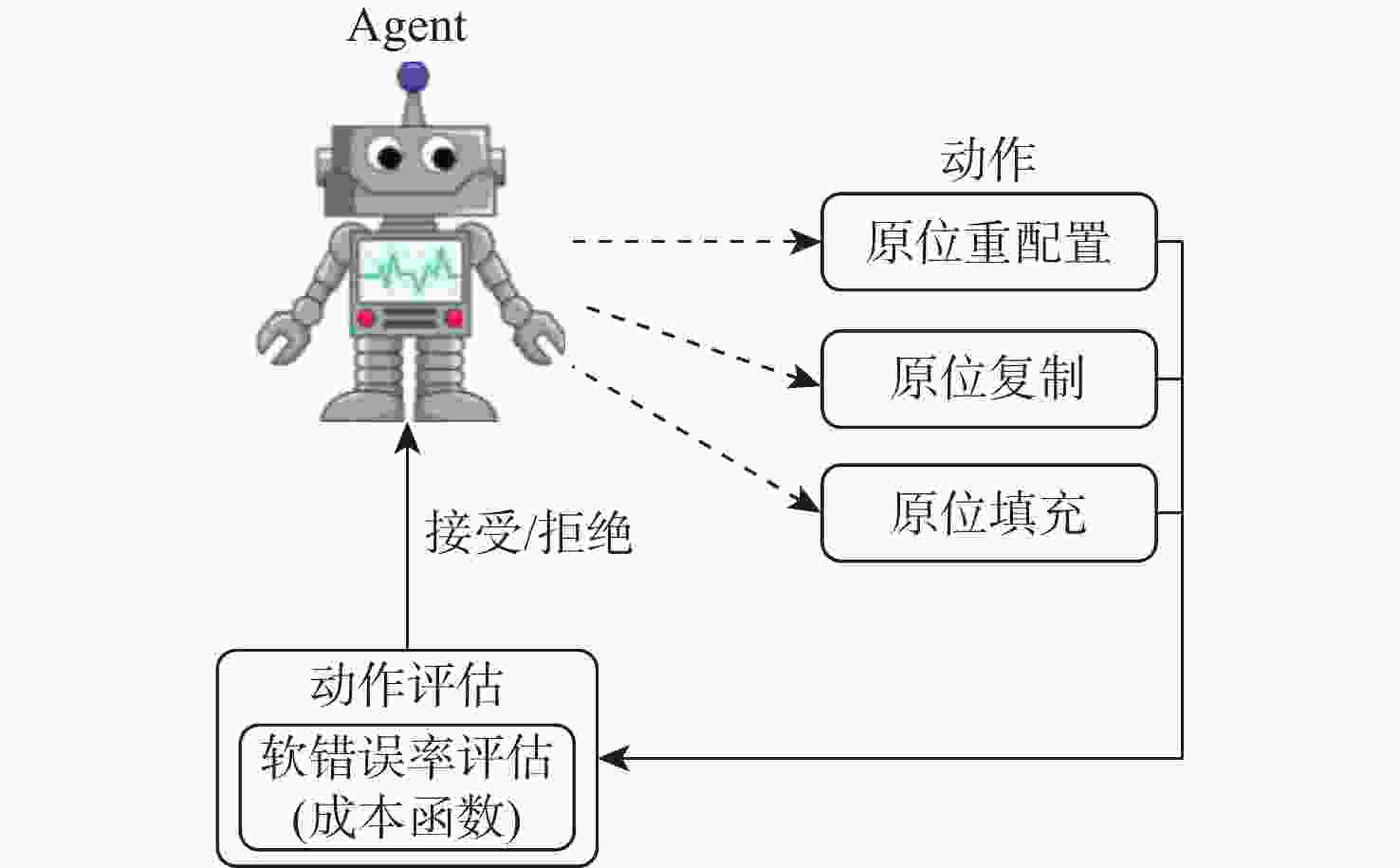

静态随机存取存储器(SRAM)型FPGA具有开发成本低、设计周期短、通用性广等一系列优点,被广泛应用于航天、军事、高能核物理和地面通信等领域,这些应用的特殊性对FPGA器件的抗辐射性能提出了额外的需求,研究SRAM型FPGA的软错误防护方法,进而提升系统可靠性变得迫在眉睫。基于此,按硬件级别、系统级别和软件级别对各类抗辐射优化技术进行概述,梳理硬件防护、三模冗余(TMR)、动态刷新重配置、设计实现算法优化等主流技术,对各项技术的优势和劣势进行分析,并阐述使用原位容错方法作为补充技术,对三模冗余加动态刷新重配置技术后的FPGA设计进行进一步加固的可行性和必要性。对机器学习技术在抗辐射优化中的应用探索做了总结和展望,并对基于强化学习的软件容错方法的架构进行了描述,以希望为进一步完善FPGA软件抗辐射措施提供技术支持,为抗辐射加固及相关领域的研究人员提供参考。

Abstract:Static random-access memory (SRAM) -based FPGAs are widely used due to their low development cost, short design cycles, and broad adaptability. In applications such as aerospace, military, high-energy nuclear physics, and terrestrial communication systems, these devices face additional requirements for radiation resistance. Therefore, studying soft error protection methods for SRAM-based FPGAs to enhance system reliability has become urgent. This paper categorizes radiation hardening techniques into three levels: hardware-level techniques, system-level techniques, and software-level techniques. It also reviews research in these categories, including hardware hardening, triple modular redundancy (TMR), scrubbing techniques, and algorithm optimization methods. The advantages and disadvantages of each technique are analyzed, and the feasibility and necessity of using in-place fault tolerance as a supplementary technique to further strengthen the TMR + scrubbing design are discussed. Finally, the paper summarizes and provides an outlook on the application of machine learning techniques in this field and proposes a software fault tolerance method based on reinforcement learning. This research aims to offer technical support for the further enhancement of FPGA software radiation resistance methods and provide a reference for researchers in radiation hardening and related fields.

-

表 1 动态刷新重配置技术分类

Table 1. Dynamic scrubbing reconfiguration techniques classification

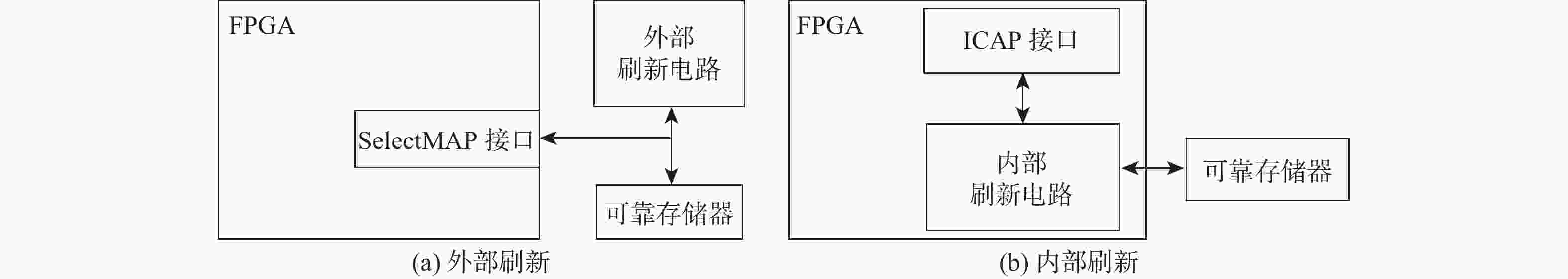

分类标准 刷新方法 优势 劣势 实现复杂度 容错效果 按刷新策略 盲刷新 实现难度低,对多粒子翻转事件有效 过多无效刷新提升了单粒子功能

中断事件的发生概率低 中 基于回读检测的刷新 减少无效刷新次数,对多粒子翻转事件有效 需要额外的比较器电路 中 高 按刷新范围 基于设备的刷新 实现难度低 过多无效刷新提升了单粒子功能

中断事件的发生概率低 中 基于帧的刷新 降低了单粒子功能中断事件的发生概率 实现复杂度上升,刷新速度减慢 中 高 按刷新时机 按时刷新 实现难度低 容错效果取决于刷新频率,

过多无效刷新,功耗较高低 中 按需刷新 容错效果好,最小化无效刷新带来的副作用 实现较复杂 较高 较高 按刷新电路位置 外部刷新 鲁棒性高 需外部电路 中 高 内部刷新 实现简单 刷新电路会受到软错误影响 较高 中 表 2 FPGA在抗辐射环境中采用的片外存储技术

Table 2. Off-chip storage techniques for FPGAs in radiation-resistant environments

存储技术 抗辐射性能 抗辐射应用 描述 抗总剂量效应能力 抗单粒子事件能力 SRAM 较强 较弱 用于片内配置位存储阵列 采用冗余设计、刷新配置等方法来提高可靠性 反熔丝 免疫 免疫 用于片内配置位存储阵列 仅能单次编程 Flash 较弱 较弱 用于片内配置位存储阵列/

用于片外存储密度高,功耗低,单器件容量达512 Mbit RRAM 强 强 用于片外存储 工作电流低,低功耗下具有高性能 MRAM 强 强 用于片内配置位存储阵列/

用于片外存储关键部件免疫辐射效应,兼容CMOS工艺,单器件容量达4 Mbit[55] FeRAM 较强 较强 用于片外存储 极强耐用性,工作电流低,单器件容量达2 Mbit[56] 表 3 细粒度三模冗余技术分类

Table 3. Fine-grained triple modular redundancy techniques classification

类别 图示说明 占用资源 容错效果 局部三模冗余

较少 较差 分布式三模冗余

平衡 平衡 全局三模冗余

较大 较好 块三模冗余

平衡 平衡 表 4 不同软件容错方法的比较

Table 4. Comparison of different software fault tolerance algorithms

容错方法 优势 劣势 占用资源 容错效果 在布局布线阶段

使用GA和PSO算法相较于VPR,软错误率降低35% 关键路径增长11%,线长增加14% 中高 中 RoRA算法 相较于三模冗余,容错效果显著提升 相较于三模冗余,布线资源增长8%~38%,

平均性能下降22%高 高 ROSE算法 相较于ABC,查找表减少1%,软错误

率降低25%运行时间长,单独使用容错效果不足 低 中低 IPR方法 相较于ABC,软错误率降低48% 单独使用容错效果不足 低 中 IPF方法 相较于ABC,软错误率降低15% 单独使用容错效果不足 低 中低 R2方法 相较于IPR方法,布线资源减少5%,

MTTF提升24%对电路拓扑结构改变较大 低 中 IPD方法 相较于ABC,软错误率最高下降53% 仅针对查找表进行容错加固,并未加固

布线资源低 中 IPV方法 相较于ABC,软错误率下降61% 基于FPGA学术模型,与商业化FPGA有

原理级差异低 中 表 5 不同软件容错方法组合的比较

Table 5. Comparison of different combinations of software fault tolerance algorithms

方法组合 对查找表配置位的

优化效果/%对电路级配置位的

优化效果/%IPF+IPD 66.53 19.63 IPF+IPV 17.58 66.29 IPD+IPV 74.34 67.33 IPF+IPD+IPV 66.53 70.24 -

[1] KASTENSMIDT F, RECH P. FPGAs and parallel architectures for aerospace applications: soft errors and fault-tolerant design[M]. Berlin: Springer , 2016. [2] 吴正新. 航天器舱内辐射环境及空间剂量学应用研究[D]. 长春: 吉林大学, 2020.WU Z X. Study on radiation environment in spacecraft cabin and application of space dosimetry[D]. Changchun: Jilin University, 2020(in Chinese). [3] QUINN H, GRAHAM P. Terrestrial-based radiation upsets: a cautionary tale[C]//Proceedings of the 13th Annual IEEE Symposium on Field-Programmable Custom Computing Machines. Piscataway: IEEE Press, 2005: 193-202. [4] ROED K. Single event upsets in SRAM FPGA based readout electronics for the time projection chamber in the ALICE experiment[D]. Bergen: University of Bergen, 2009. [5] KASAP S, WÄCHTER E W, ZHAI X J, et al. Survey of soft error mitigation techniques applied to LEON3 soft processors on SRAM-based FPGAs[J]. IEEE Access, 2020, 8: 28646-28658. doi: 10.1109/ACCESS.2020.2969714 [6] KELLER A M, WIRTHLIN M J. Impact of soft errors on large-scale FPGA cloud computing[C]//Proceedings of the ACM/SIGDA International Symposium on Field-Programmable Gate Arrays. New York: ACM, 2019: 272-281. [7] European Cooperation for Space Standardization. Space engineering-method for the calculation of radiation received and its effects, and a policy for design margins: 2014: DIN EN 16603-10-12[S]. [S.l.]: European Cooperation for Space Standardization, 2014. [8] TOWNSEND L W, ADAMS J H, BLATTNIG S R, et al. Solar particle event storm shelter requirements for missions beyond low Earth orbit[J]. Life Sciences in Space Research, 2018, 17: 32-39. doi: 10.1016/j.lssr.2018.02.002 [9] SIEGLE F, VLADIMIROVA T, ILSTAD J, et al. Mitigation of radiation effects in SRAM-based FPGAs for space applications[J]. ACM Computing Surveys, 2015, 47(2): 1-34. [10] BOULGHASSOUL Y, BAJURA M, STANSBERRY S, et al. TID damage and annealing response of 90 nm commercial-density SRAMs[C]//Proceedings in European Conference on Radiation and Its Effects on Components and Systems. [S.l.:s.n.] , 2008: 274-279. [11] 范晓洋. 不同阈值FDSOI器件总剂量效应及其加固技术研究[D]. 西安: 西安电子科技大学, 2022.FAN X Y. Research on total dose effect and reinforcement technology of FDSOI devices with different thresholds[D]. Xi’an: Xidian University, 2022(in Chinese). [12] 薛玉雄, 杨生胜, 陈罗婧, 等. 空间单粒子锁定效应研究[J]. 核技术, 2012, 35(9): 692-697.XUE Y X, YANG S S, CHEN L J, et al. Investigation of single event latchup[J]. Nuclear Techniques, 2012, 35(9): 692-697(in Chinese). [13] 杨世宇, 曹洲, 薛玉雄. 空间单粒子锁定及防护技术研究[J]. 核电子学与探测技术, 2008, 28(5): 945-948. doi: 10.3969/j.issn.0258-0934.2008.05.019YANG S Y, CAO Z, XUE Y X. Research on the single event latchup in the space and it’s protection technology[J]. Nuclear Electronics & Detection Technology, 2008, 28(5): 945-948(in Chinese). doi: 10.3969/j.issn.0258-0934.2008.05.019 [14] DODD P E, MASSENGILL L W. Basic mechanisms and modeling of single-event upset in digital microelectronics[J]. IEEE Transactions on Nuclear Science, 2003, 50(3): 583-602. doi: 10.1109/TNS.2003.813129 [15] TAWFEEK R M, EGILA M G, ALKABANI Y, et al. A survey on faults and mitigation techniques in FPGAs[C]//Proceedings of the IEEE 4th International Conference on New PARADIGMS in Electronics & Information Technology. Piscataway: IEEE Press, 2017. [16] HASS K J, AMBLES J W. Single event transients in deep submicron CMOS[C]//Proceedings of the 42nd Midwest Symposium on Circuits and Systems. Piscataway: IEEE Press, 2002: 122-125. [17] JEDEC. Single-event transient (SET)[EB/OL]. [2023-06-16]. https://www.jedec.org/standards-documents/dictionary/terms/single-event-transient-set. [18] JEDEC. Single-event functional interrupt (SEFI)[EB/OL]. [2023-06-16]. https://www.jedec.org/standards-documents/dictionary/terms/single-event-functional-interrupt-sefi. [19] RICK P. Reconfigurable FPGAs in space-present and future[C]//Proceedings of the Military and Aerospace Programmable Logic Devices Conference. [S.l.]: MAPLD, 2005. [20] VISSERS K. Keynote 2: versal: the new Xilinx adaptive compute acceleration platforms[C]//Proceedings of the IEEE/ACM 8th Workshop on Irregular Applications: Architectures and Algorithms. Piscataway: IEEE Press, 2018. [21] Microchip. FPGA radiation & reliability data[EB/OL]. [2023-06-16]. https://www.microsemi.com/product-directory/rad-tolerant-fpgas/1698-radiation-reliability-data. [22] 曹正州, 张艳飞, 徐玉婷, 等. 基于反熔丝技术的FPGA配置芯片设计[J]. 电子与封装, 2021, 21(12): 70-76.CAO Z Z, ZHANG Y F, XU Y T, et al. Design of FPGA configuration chip based on anti-fuse technology[J]. Electronic & Packaging, 2021, 21(12): 70-76(in Chinese). [23] Microchip. PolarFire® mid-range FPGAs[EB/OL]. [2023-06-16]. https://www.microchip.com/en-us/products/fpgas-and-plds/fpgas/polarfire-fpgas/polarfire-mid-range-fpgas. [24] NICOLAIDIS M. Soft errors in modern electronic systems[M]. Berlin: Springer, 2010. [25] GONÇALVES O, PRENAT G, DIENY B. Radiation hardened MRAM-based FPGA[J]. IEEE Transactions on Magnetics, 2013, 49(7): 4355-4358. doi: 10.1109/TMAG.2013.2247744 [26] RAJAEI R. Radiation-hardened design of nonvolatile MRAM-based FPGA[J]. IEEE Transactions on Magnetics, 2016, 52(10): 3402010. [27] 蔡畅. 纳米SRAM型FPGA的单粒子效应及其加固技术研究[D]. 兰州: 中国科学院大学(中国科学院近代物理研究所), 2021.CAI C. Research on single event effect and reinforcement technology of nano-SRAM FPGA[D]. Lanzhou: University of Chinese Academy of Sciences (Institute of Modern Physics, Chinese Academy of Sciences), 2021(in Chinese). [28] BHUVANESHWARI Y V, SAI N P, KUMAR N V, et al. SEU study of 4T, 6T, 7T, 8T, 10T MOSFET based SRAM using TCAD simulation[C]//Proceedings of the International Conference on Information Communication and Embedded Systems. Piscataway: IEEE Press, 2014: 1-7. [29] LI T H, YANG Y T, ZHANG J N, et al. A novel SEU hardened SRAM bit-cell design[J]. IEICE Electronics Express, 2017, 14(12): 20170413. doi: 10.1587/elex.14.20170413 [30] SHEN Z T, FENG C Q, GAO S S, et al. Study on FPGA SEU mitigation for the readout electronics of dampe BGO Calorimeter in space[J]. IEEE Transactions on Nuclear Science, 2015, 62(3): 1010-1015. doi: 10.1109/TNS.2015.2427293 [31] SECONDO R, FOUCARD G, DANZECA S, et al. Embedded detection and correction of SEU bursts in SRAM memories used as radiation detectors[J]. IEEE Transactions on Nuclear Science, 2016, 63(4): 2168-2175. doi: 10.1109/TNS.2016.2521485 [32] STERPONE L, REORDA M S, VIOLANTE M. RoRA: a reliability-oriented place and route algorithm for SRAM-based FPGAs[C]//Proceedings of the Research in Microelectronics and Electronics. Piscataway: IEEE Press, 2005: 173-176. [33] HU Y, FENG Z, HE L, et al. Robust FPGA resynthesis based on fault-tolerant Boolean matching[C]//Proceedings of the IEEE/ACM International Conference on Computer-Aided Design. Piscataway: IEEE Press, 2008: 706-713. [34] FENG Z, HU Y, HE L, et al. IPR: in-place reconfiguration for FPGA fault tolerance? [C]//Proceedings of the International Conference on Computer-Aided Design. New York: ACM, 2009: 105-108. [35] JOSE M, HU Y, MAJUMDAR R, et al. Rewiring for robustness[C]//Proceedings of the 47th Design Automation Conference. New York: ACM, 2010: 469-474. [36] LEE J Y, FENG Z, HE L. In-place decomposition for robustness in FPGA[C]//Proceedings of the IEEE/ACM International Conference on Computer-Aided Design. Piscataway: IEEE Press, 2010: 143-148. [37] JING N F, LEE J Y, HE W F, et al. Mitigating FPGA interconnect soft errors by in-place LUT inversion[C]//Proceedings of the IEEE/ACM International Conference on Computer-Aided Design. Piscataway: IEEE Press, 2011: 582-586. [38] FENG Z, JING N F, HE L. IPF: in-place X-filling algorithm for the reliability of modern FPGAs[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22(10): 2226-2229. [39] 黄影, 张春元, 刘东. SRAM型FPGA的抗SEU方法研究[J]. 中国空间科学技术, 2007, 27(4): 57-65. doi: 10.3321/j.issn:1000-758X.2007.04.010HUANG Y, ZHANG C Y, LIU D. Research on SEU mitigation of FPGA based-on SRAM[J]. Chinese Space Science and Technology, 2007, 27(4): 57-65(in Chinese). doi: 10.3321/j.issn:1000-758X.2007.04.010 [40] PRATT B, CAFFREY M, GRAHAM P, et al. Improving FPGA design robustness with partial TMR[C]//Proceedings of the IEEE International Reliability Physics Symposium Proceedings. Piscataway: IEEE Press, 2006: 226-232. [41] SAMUDRALA P K, RAMOS J, KATKOORI S. Selective triple Modular redundancy (STMR) based single-event upset (SEU) tolerant synthesis for FPGAs[J]. IEEE Transactions on Nuclear Science, 2004, 51(5): 2957-2969. doi: 10.1109/TNS.2004.834955 [42] 张瑶伟. 基于高层次综合的三模冗余软件技术研究[D]. 北京: 中国运载火箭技术研究院, 2022.ZHANG Y W. Research of software technology for triple modular redundancy based on high level synthesis[D]. Beijing: China Academy of Launch Vehicle Technology, 2022(in Chinese). [43] LEE D S, KING M, EVANS W, et al. Single-event characterization of 16 nm FinFET Xilinx ultrascale devices with heavy ion and neutron irradiation[C]//Proceedings of the IEEE Radiation Effects Data Workshop. Piscataway: IEEE Press, 2018: 1-8. [44] 陈雷. 百万门级FPGA芯片设计技术及辐射加固技术研究[D]. 北京: 中国空间技术研究院, 2010.CHEN L. Research on million-gate level FPGA chip design and radiation-hardening techniques[D]. Beijing: China Academy of Space Technology, 2010(in Chinese). [45] PENG C Y, HUANG J T, LIU C Y, et al. Radiation-hardened 14T SRAM bitcell with speed and power optimized for space application[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2019, 27(2): 407-415. doi: 10.1109/TVLSI.2018.2879341 [46] AHMED A. New FPGA blind scrubbing technique[C]//Proceedings of the IEEE Aerospace Conference. Piscataway: IEEE Press, 2016: 1-9. [47] BRIDGFORD B, CARMICHAEL C, TSENG C W. Correcting single-event upsets in Virtex-II platform FPGA configuration memory[EB/OL]. [2023-09-01]. https://docs.amd.com/v/u/en-US/xapp779. [48] Xilinx. Virtex-5 FPGA configuration user guide[EB/OL]. (2023-02-21) [2023-06-19]. https://docs.xilinx.com/v/u/en-US/ug191. [49] SIEGLE F, VLADIMIROVA T, EMAM O, et al. Adaptive FDIR framework for payload data processing systems using reconfigurable FPGAs[C]//Proceedings of the NASA/ESA Conference on Adaptive Hardware and Systems. Piscataway: IEEE Press, 2013: 15-22. [50] MOUSAVI M, POURSHAGHAGHI H R, KUMAR A, et al. MTTR reduction of FPGA scrubbing: exploring SEU sensitivity[J]. Microprocessors and Microsystems, 2023, 101: 104841. doi: 10.1016/j.micpro.2023.104841 [51] STODDARD A, GRUWELL A, ZABRISKIE P, et al. A hybrid approach to FPGA configuration scrubbing[J]. IEEE Transactions on Nuclear Science, 2017, 64(1): 497-503. doi: 10.1109/TNS.2016.2636666 [52] MILLER A G, CARMICHAEL C, SWIFT G. Single-event upset mitigation for Xilinx FPGA block memories[EB/OL]. [2023-09-01]. https://docs.amd.com/v/u/en-US/xapp962. [53] 钟敏. SRAM型FPGA的SEU容错技术研究[D]. 北京: 中国科学院大学(中国科学院光电技术研究所), 2021.ZHONG M. Research on SEU fault tolerance technology of SRAM FPGA[D]. Beijing: University of Chinese Academy of Sciences (Institute of Optics and Electronics, Chinese Academy of Sciences), 2021(in Chinese). [54] Infineon Technologies AG. Infineon 256Mb 512Mb rad tolerant nor flash product brief[EB/OL]. (2022-02-17) [2023-12-15]. https://www.infineon.com/dgdl/Infineon-256Mb_512Mb-Rad-tolerant-NOR-Flash-ProductBrief-v01_00-EN.pdf?fileId=8ac78c8c7e7124d1017ee46ab85b1c18. [55] Everspin. Case study: SpriteSat (Rising) satellite[EB/OL]. [2023-12-15]. https://www.everspin.com/aerospace. [56] Infineon Technologies AG. Infineon F-RAM solutions product brochure[EB/OL]. (2022-02-15) [2023-12-15]. https://www.infineon.com/dgdl/Infineon-F-RAM_Solutions-ProductBrochure-v04_00-EN.pdf?fileId=8ac78c8c7d0d8da4017d0f64d6975061. [57] 张超, 赵伟, 刘峥. 基于FPGA的三模冗余容错技术研究[J]. 现代电子技术, 2011, 34(5): 167-171. doi: 10.3969/j.issn.1004-373X.2011.05.051ZHANG C, ZHAO W, LIU Z. Research of TMR-based fault-tolerance techniques based on FPGA[J]. Modern Electronics Technique, 2011, 34(5): 167-171(in Chinese). doi: 10.3969/j.issn.1004-373X.2011.05.051 [58] BENITES L A C, KASTENSMIDT F L. Automated design flow for applying triple modular redundancy (TMR) in complex digital circuits[C]//Proceedings of the IEEE 19th Latin-American Test Symposium. Piscataway: IEEE Press, 2018: 1-4. [59] BENITES L A C, BENEVENUTI F, DE OLIVEIRA Á B, et al. Reliability calculation with respect to functional failures induced by radiation in TMR arm cortex-M0 soft-core embedded into SRAM-based FPGA[J]. IEEE Transactions on Nuclear Science, 2019, 66(7): 1433-1440. doi: 10.1109/TNS.2019.2921796 [60] BENEVENUTI F, CHIELLE E, TONFAT J, et al. Experimental applications on SRAM-based FPGA for the NanosatC-BR2 scientific mission[C]//Proceedings of the IEEE International Parallel and Distributed Processing Symposium Workshops. Piscataway: IEEE Press, 2019: 140-146. [61] 陈雷, 张瑶伟, 王硕, 等. FPGA三模冗余工具的关键技术与发展[J]. 电子与信息学报, 2022, 44(6): 2230-2244.CHEN L, ZHANG Y W, WANG S, et al. Key technology and development of triple modular redundancy tool for FPGA[J]. Journal of Electronics & Information Technology, 2022, 44(6): 2230-2244(in Chinese). [62] PRATT B, WIRTHLIN M, CAFFREY M, et al. Improving FPGA reliability in harsh environment using triple modular redundancy with more frequent voting[C]//Proceedings of the Military and Aerospace FPGA and Applications Meeting. [S.l.:s.n.], 2007. [63] CANNON M J. Improving the single event effect response of triple modular redundancy on SRAM FPGAs through placement and routing[D]. Provo: Brigham Young University, 2019. [64] KHATRI A R, HAYEK A, BORCSOK J. RASP-TMR: an automatic and fast synthesizable verilog code generator tool for the implementation and evaluation of TMR approach[J]. International Journal of Advanced Computer Science and Applications, 2018, 9(8): 590-597. [65] LEE G, AGIAKATSIKAS D, WU T, et al. TLegUp: a TMR code generation tool for SRAM-based FPGA applications using HLS[C]//Proceedings of the IEEE 25th Annual International Symposium on Field-Programmable Custom Computing Machines. Piscataway: IEEE Press, 2017: 129-132. [66] 田春生, 陈雷, 王硕, 等. BFDS: BMTI FPGA设计套件[C]//中国航天科技集团有限公司科技委“微电子与元器件应用专业组”与“航天计算机专业组”2021年联合学术年会. 上海: 中国航天科技集团有限公司科技委, 2021: 1-10.TIAN C S, CHEN L, WANG S, et al. BFDS: MBTI FPGA design suite[C]//Joint Annual Academic Conference 2021 of the Microelectronics and Component Applications Specialized Group and the Aerospace Computer Specialized Group. Shanghai: The Science and Technology Committee of China Aerospace Science and Technology Corporation, 2021: 1-10(in Chinese). [67] KELLER A M. Partial circuit replication for masking and detecting soft errors in SRAM-based FPGAs[D]. Provo: Brigham Young University, 2021. [68] STERPONE L, VIOLANTE M. A new reliability-oriented place and route algorithm for SRAM-based FPGAs[J]. IEEE Transactions on Computers, 2006, 55(6): 732-744. doi: 10.1109/TC.2006.82 [69] JAHANIRAD H, MOHAMMADI K. Reliable implementation on SRAM-based FPGA using evolutionary methods[J]. IETE Journal of Research, 2013, 59(5): 597. doi: 10.4103/0377-2063.123766 [70] STERPONE L, BATTEZZATI N, VIOLANTE M. A new placement algorithm for the optimization of fault tolerant circuits on reconfigurable devices[C]//Proceedings of the Workshop on Radiation Effects and Fault Tolerance in Nanometer Technologies. New York: ACM, 2008: 347-352. [71] 张双悦. 一种FPGA综合过程中的测试向量生成与可测性设计方法[D]. 北京: 清华大学, 2014.ZHANG S Y. A test vector generation and testability design method in FPGA synthesis process[D]. Beijing: Tsinghua University, 2014(in Chinese). [72] 景乃锋. 面向SRAM型FPGA软错误的可靠性评估与容错算法研究[D]. 上海: 上海交通大学, 2012.JING N F. Research on reliability evaluation and fault-tolerant algorithm for soft errors of SRAM FPGA[D]. Shanghai: Shanghai Jiao Tong University, 2012(in Chinese). [73] 孙雷, 段哲民, 刘增荣, 等. SRAM型FPGA单粒子辐照试验系统技术研究[J]. 计算机工程与应用, 2014, 50(1): 49-52. doi: 10.3778/j.issn.1002-8331.1208-0196SUN L, DUAN Z M, LIU Z R, et al. Study of SEU radiation experimental system technology of SRAM-based FPGA[J]. Computer Engineering and Applications, 2014, 50(1): 49-52(in Chinese). doi: 10.3778/j.issn.1002-8331.1208-0196 [74] ZHOU J, CHEN L, WANG S. Precision fault injection method based on correspondence between configuration bitstream and architecture (abstract only)[C]//Proceedings of the ACM/SIGDA International Symposium on Field Programmable Gate Arrays. New York: ACM, 2013: 267. [75] REORDA M S, VIOLANTE M. Accurate and efficient analysis of single event transients in VLSI circuits[C]//Proceedings of the 9th IEEE On-Line Testing Symposium. Piscataway: IEEE Press, 2003: 101-105. [76] WROBEL F, SAIGNÉ F. MC-ORACLE: a tool for predicting soft error rate[J]. Computer Physics Communications, 2011, 182(2): 317-321. doi: 10.1016/j.cpc.2010.10.005 [77] LUCKENBILL S, LEE J Y, HU Y, et al. RALF: reliability analysis for logic faults: an exact algorithm and its applications[C]//Proceedings of the Design, Automation & Test in Europe Conference & Exhibition. Piscataway: IEEE Press, 2010: 783-788. [78] KRISHNASWAMY S, VIAMONTES G F, MARKOV I L, et al. Accurate reliability evaluation and enhancement via probabilistic transfer matrices[C]//Proceedings of the Design, Automation and Test in Europe. Piscataway: IEEE Press, 2005: 282-287. [79] CONG J, MINKOVICH K. LUT-based FPGA technology mapping for reliability[C]//Proceedings of the Design Automation Conference. Piscataway: IEEE Press, 2010: 517-522. [80] ASADI G, TAHOORI M B. Soft error rate estimation and mitigation for SRAM-based FPGAs[C]//Proceedings of the ACM/SIGDA 13th International Symposium on Field-Programmable Gate Arrays. New York: ACM, 2005: 149-160. [81] ASADI G, TAHOORI M. An analytical approach for soft error rate estimation of SRAM-based FPGAs[C]//Proceedings of the Military and Aerospace Applications of Programmable Logic Devices. [S.l.:s.n.], 2004: 2991-2994. [82] HUANG G Y, HU J B, HE Y F, et al. Machine learning for electronic design automation: a survey[J]. ACM Transactions on Design Automation of Electronic Systems, 2021, 26(5): 1-46. [83] MAHAPATRA A, SCHAFER B C. Machine-learning based simulated annealer method for high level synthesis design space exploration[C]//Proceedings of the Electronic System Level Synthesis Conference. Piscataway: IEEE Press, 2014: 1-6. [84] TIAN C S, CHEN L, WANG Y, et al. Improving simulated annealing algorithm for FPGA placement based on reinforcement learning[C]//Proceedings of the IEEE 10th Joint International Information Technology and Artificial Intelligence Conference. Piscataway: IEEE Press, 2022: 1912-1919. [85] HAIM S, WALSH T. Restart strategy selection using machine learning techniques[C]//Proceedings of the Theory and Applications of Satisfiability Testing. Berlin: Springer, 2009: 312-325. [86] HE Z L, WU H Y, ZHANG X Y, et al. ChatEDA: a large language model powered autonomous agent for EDA[C]//Proceedings of the ACM/IEEE 5th Workshop on Machine Learning for CAD. Piscataway: IEEE Press, 2023: 1-6. [87] PERRYMAN N, WILSON C, GEORGE A. Evaluation of Xilinx versal architecture for next-gen edge computing in space[C]//Proceedings of the IEEE Aerospace Conference. Piscataway: IEEE Press, 2023: 1-11. -

下载:

下载: